**Subject Name:-**ANALOG and DIGITAL ELECTRONICS

Teacher Name: - Mr. Prasanta Kumar Parida

**Subject Code:-**

Semester- 3<sup>rd</sup>

**Branch-EEE**

**Course-B.Tech**

### **SYLLABUS CONTENTS**

### **MODULE-I(9 HOURS)**

Biasing of BJT: Fixed bias circuit, Self-bias circuit, Feedback bias circuit, Bias Stabilization. Transistor at Low Frequencies: Transistor Hybrid Model, h- parameters, Analysis of the transistor amplifier using h-parameter. Emitter Follower, Miller's theorem and its dual, cascading transistor amplifiers, Simplified CE and CC configurations. Transistor at high frequency: Hybrid-pi CE Transistor Model.

### **MODULE-II (6 HOURS)**

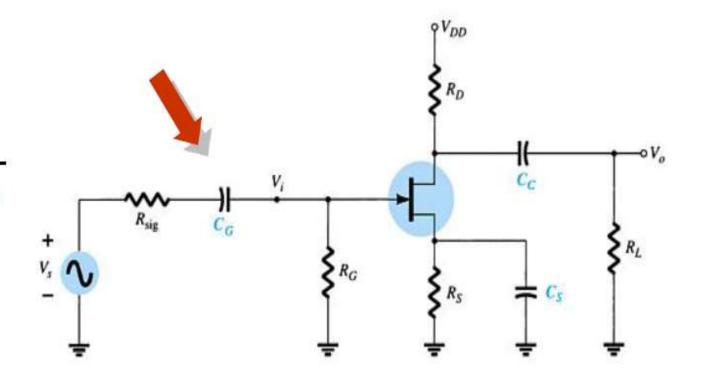

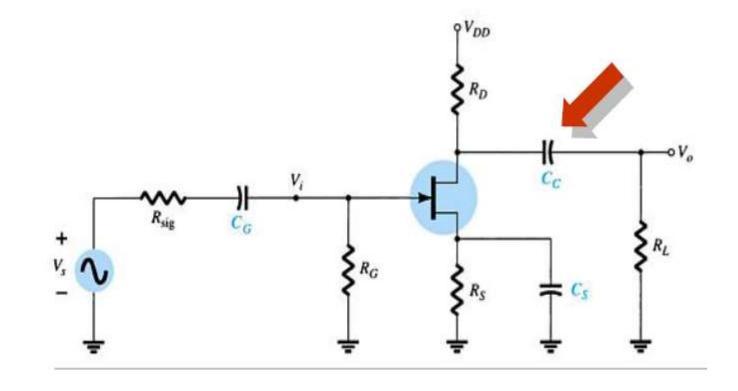

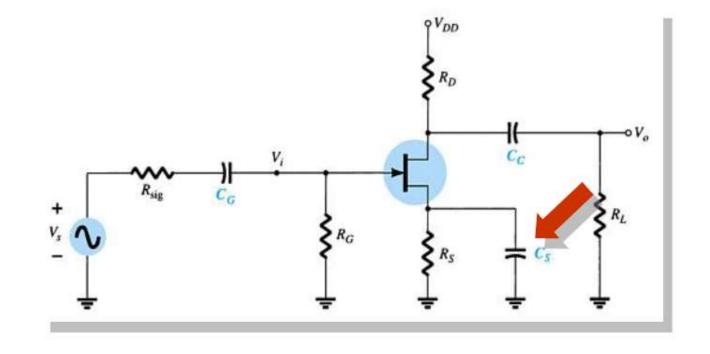

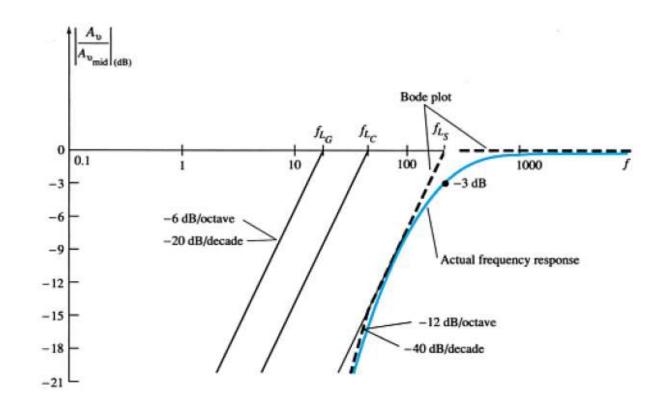

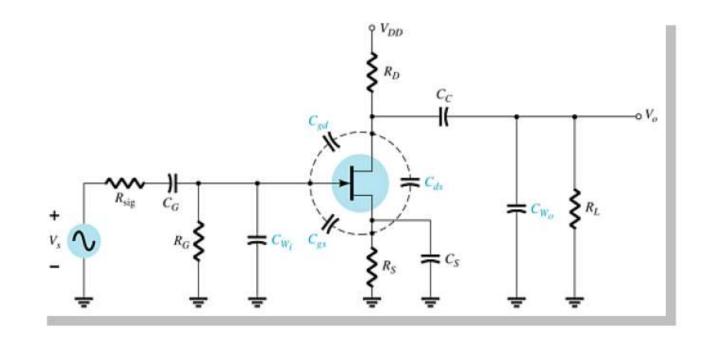

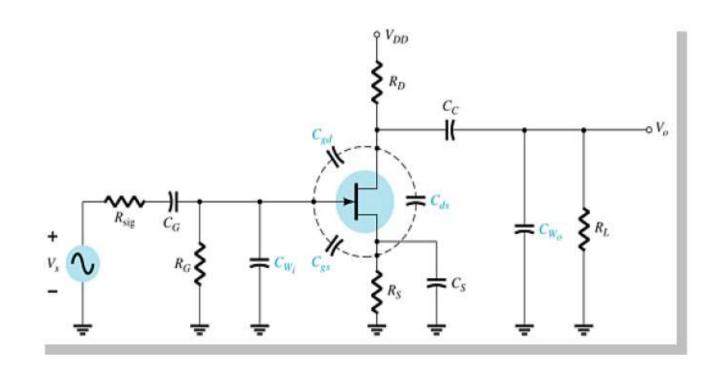

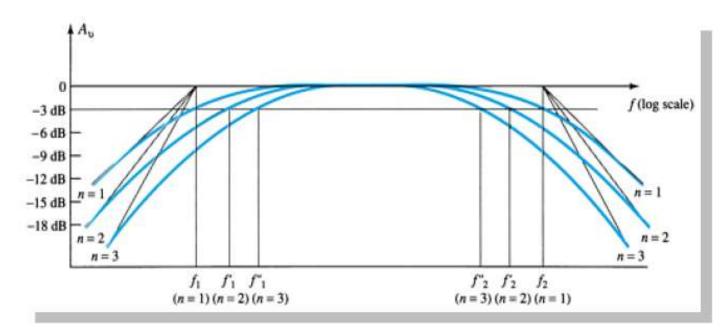

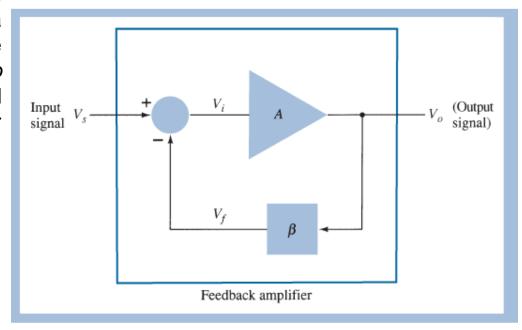

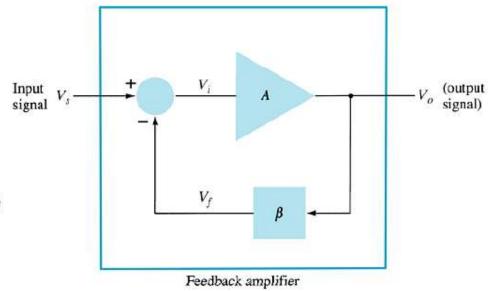

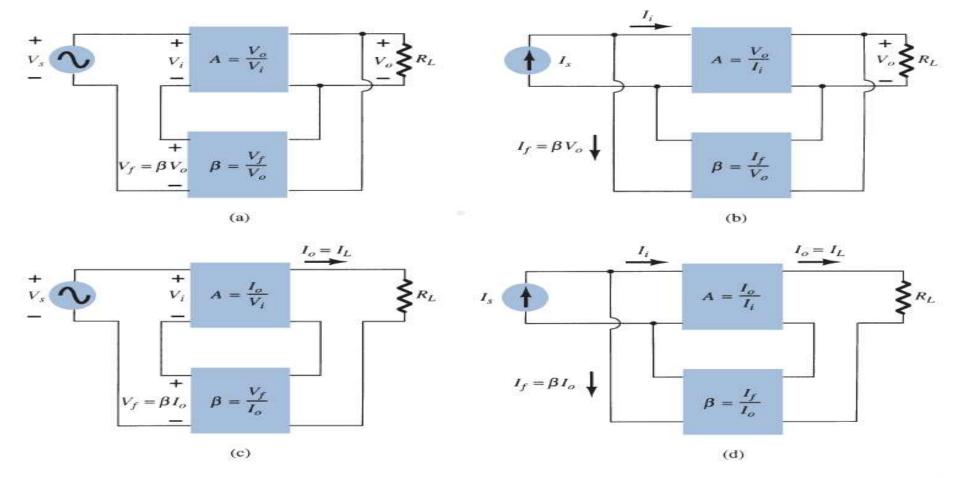

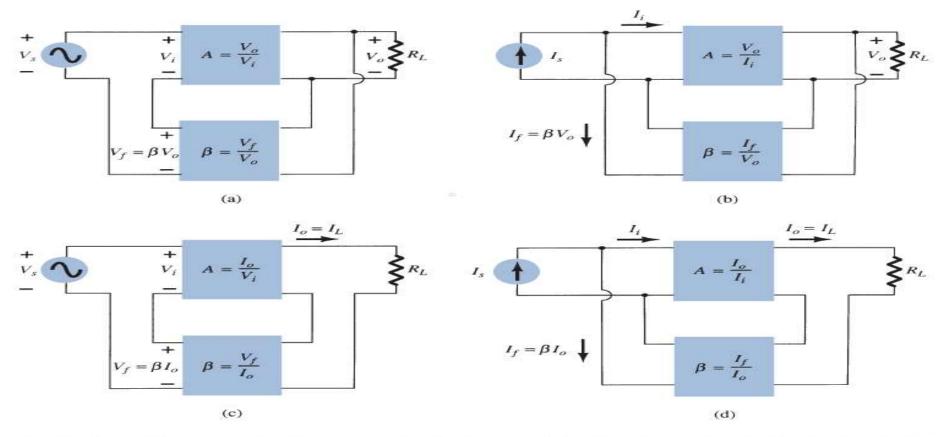

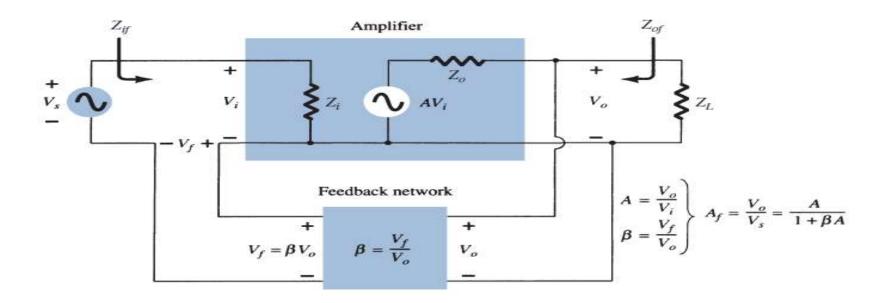

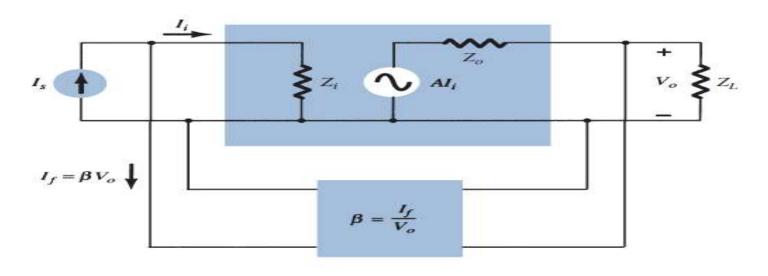

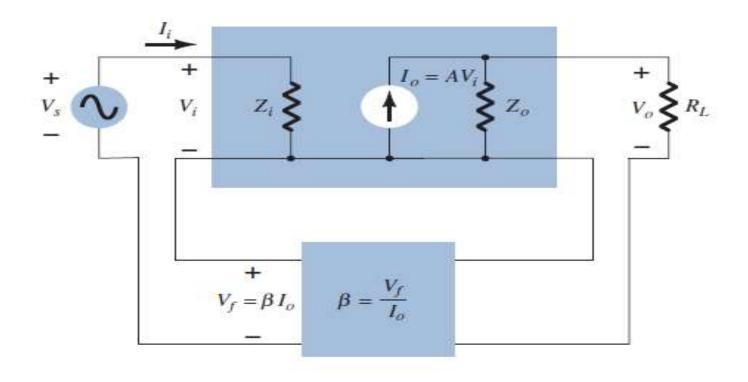

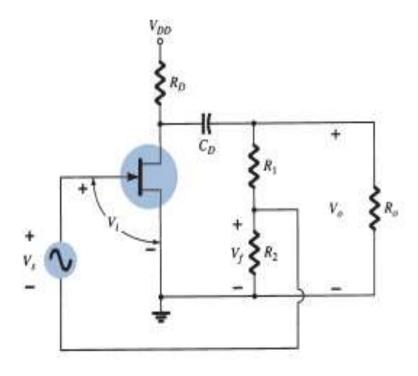

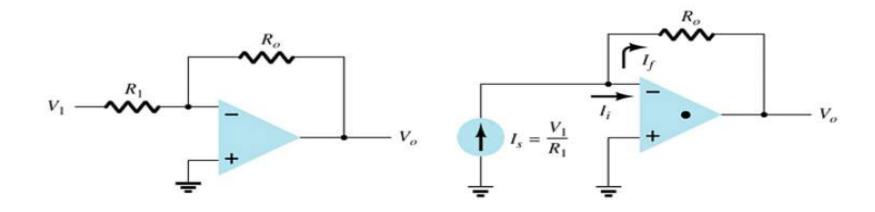

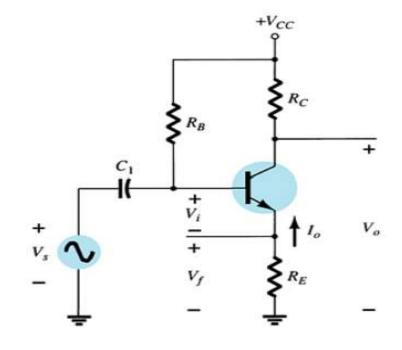

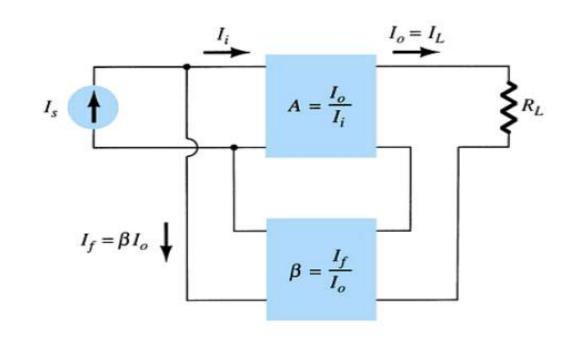

▶ Biasing the JFET: FET in fixed bias, self-bias and feedback bias configurations. FET small signal modelling. Frequency response of an amplifier, Bode plot, Band pass of cascaded stages, RC-Coupled amplifier and its low frequency response. Classification of amplifier, Feedback concept, Transfer gain, Negative feedback, Input-output resistance, Method of analysis of a feedback amplifier, Voltage series feedback, Current series feedback, Voltage shunt feedback, Current shunt feedback.

### **MODULE-III (9 HOURS)**

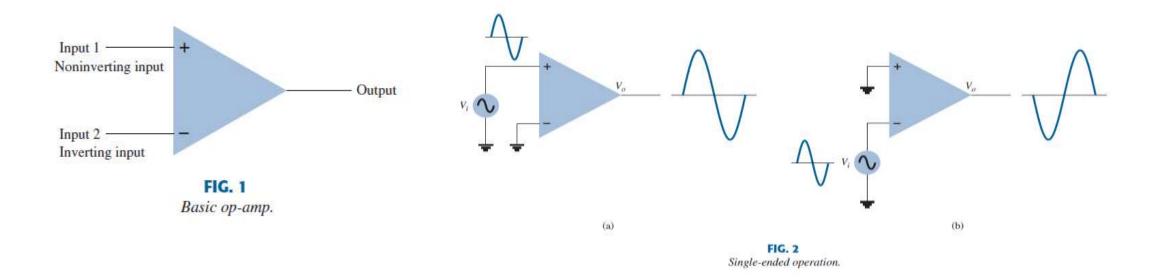

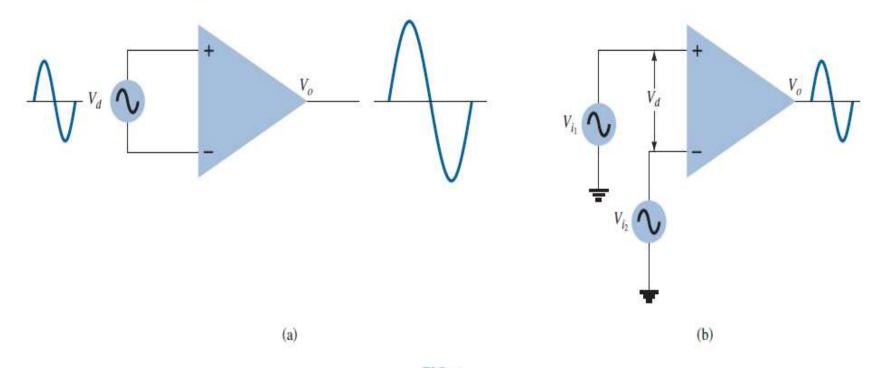

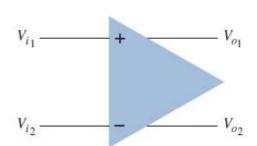

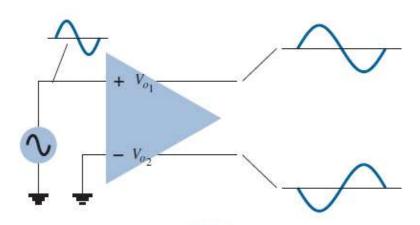

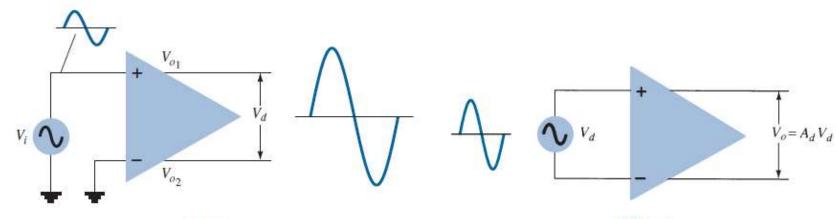

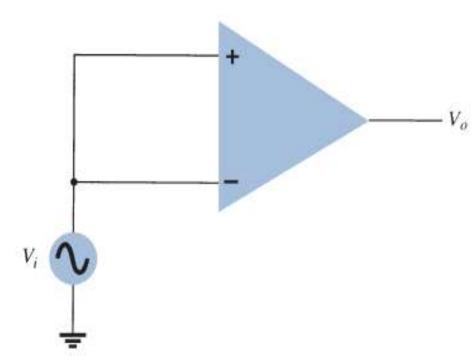

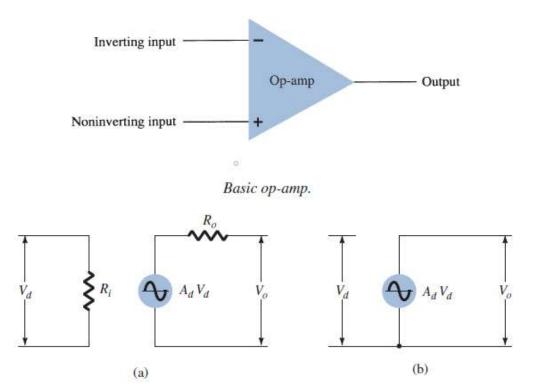

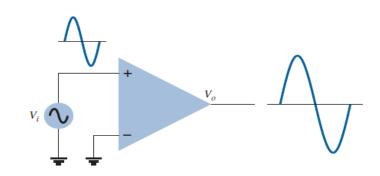

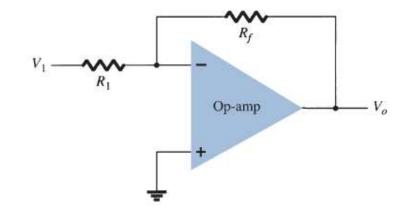

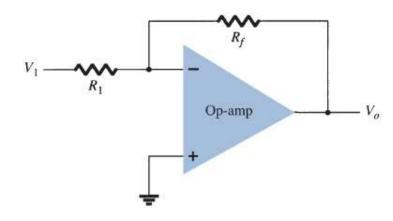

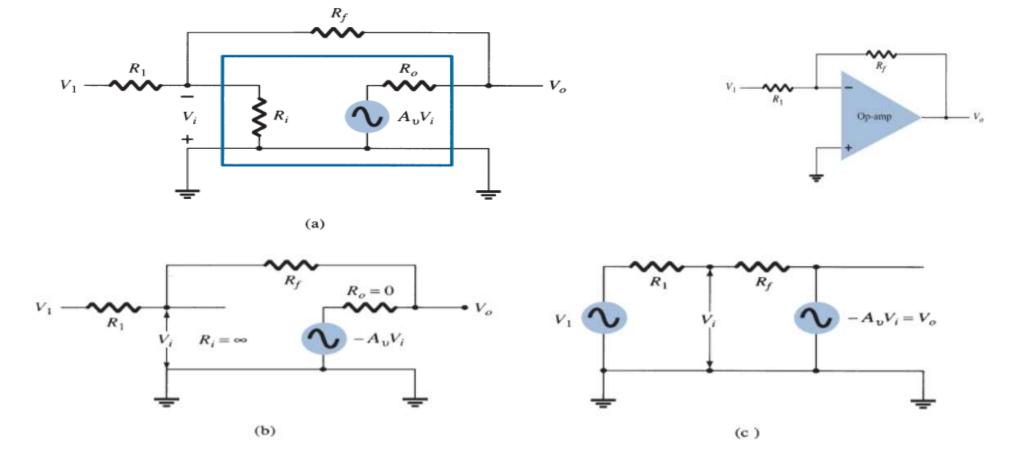

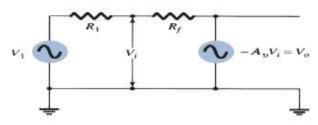

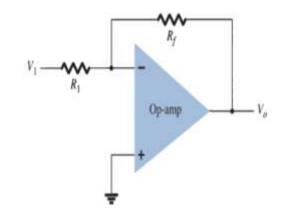

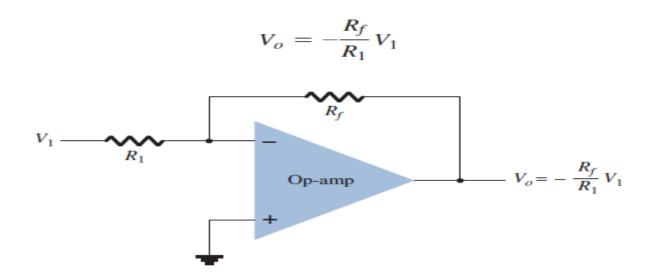

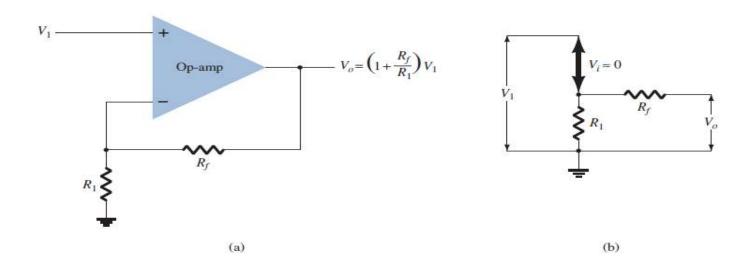

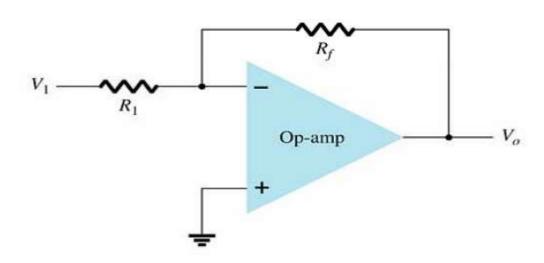

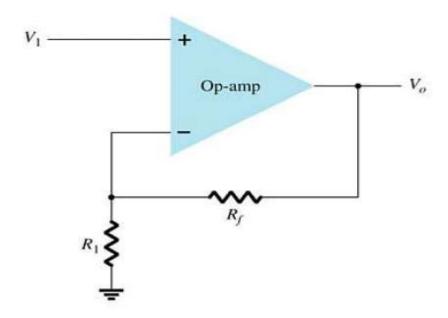

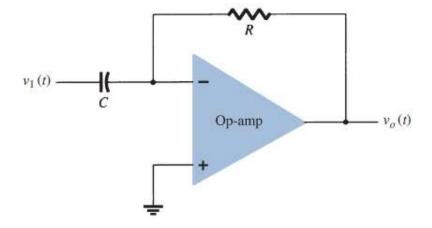

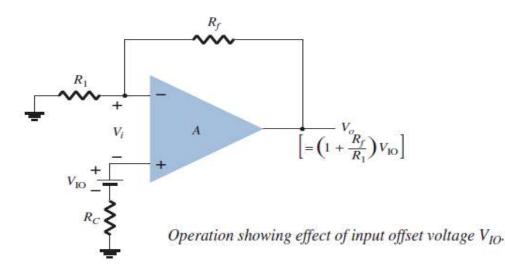

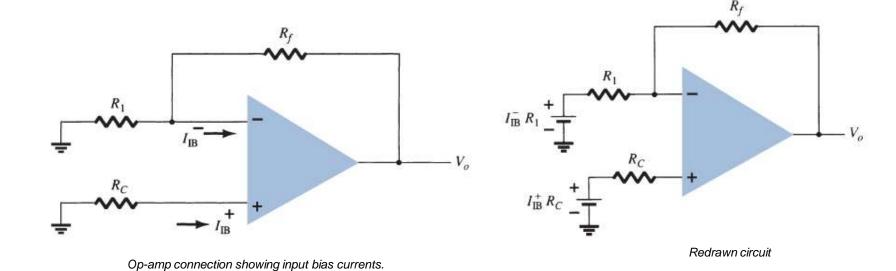

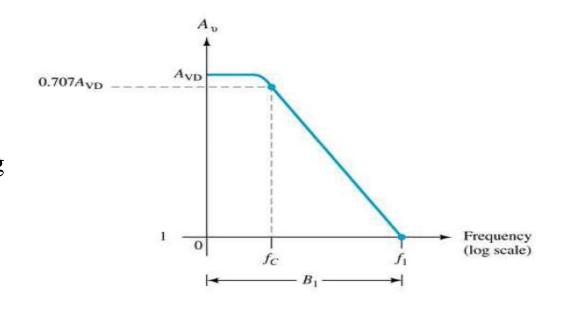

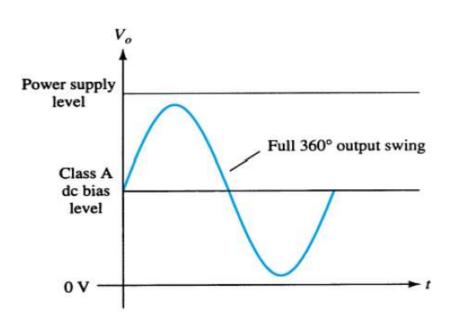

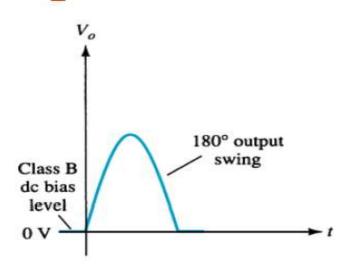

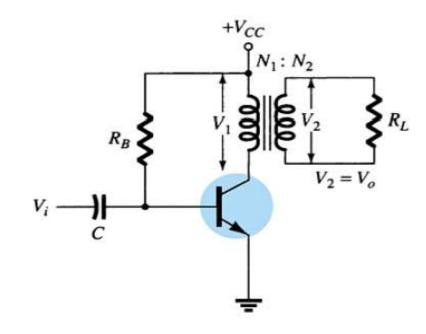

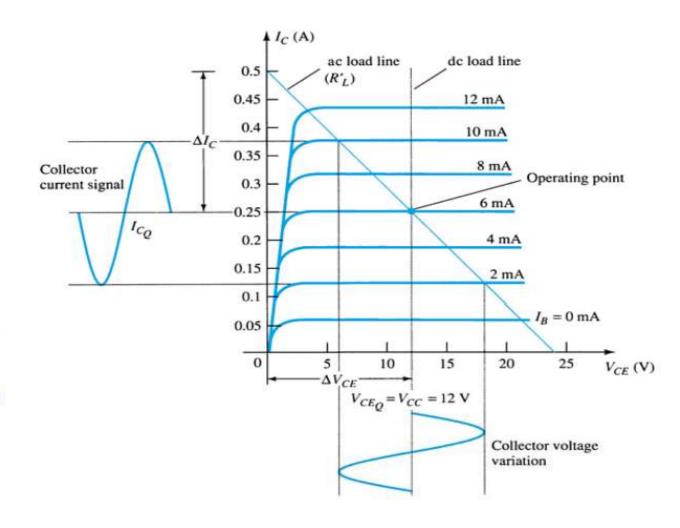

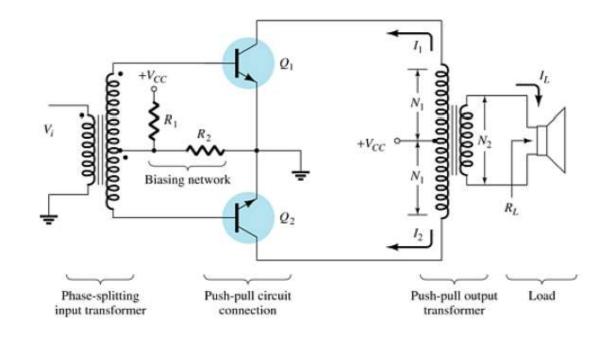

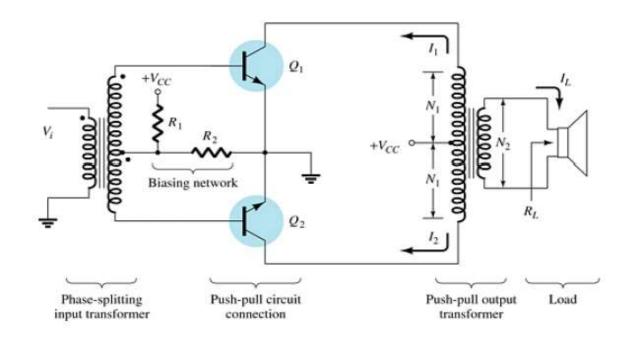

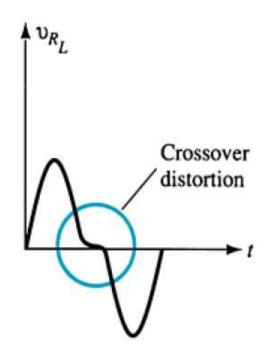

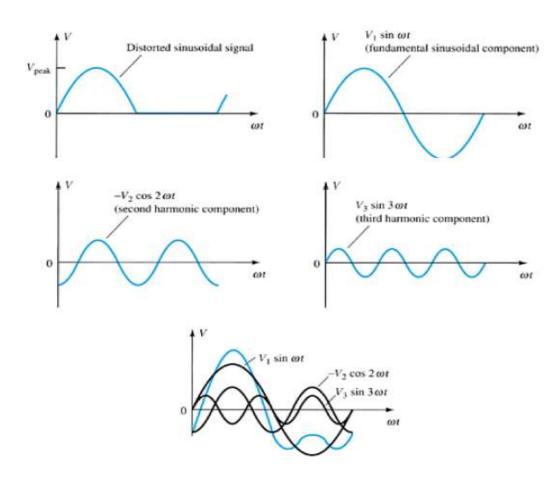

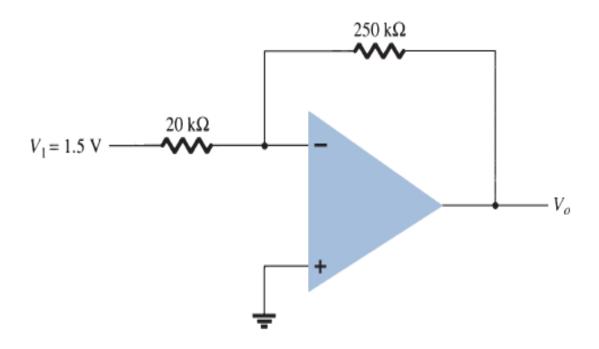

► The basic operational amplifier (OPAMP), Off-set error voltages and currents, temperature drift of input offset voltage and current, measurement of OPAMP parameters and its frequency response. Class —A large signal amplifier, higher order harmonic generation, Transformer coupled audio amplifier, push-pull amplifier.

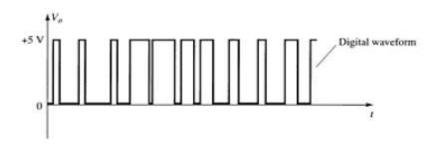

Digital circuits: Digital (Binary) operation of a system, OR gate, AND gate, NOT or inverter circuit, De Morgan's laws, NAND and NOR DTL gates, HTL gate, TTL gate, RTL and DCTL.

### **► MODULE-IV (6 HOURS)**

Binary codes: BCD codes, gray codes, ASCII Character Code, Boolean Algebra & Logic gates: Axiomatic definition of Boolean algebra. Property of Boolean algebra, Boolean functions, Canonical & standard form; min terms & max terms, standard forms; Digital Logic Gates, Multiple inputs. Gate level Minimization: The Map Method, K Map up to five variables, Product of Sum simplification, Sum of Product simplification, Don't care conditions.

### **MODULE-V** (9 HOURS)

Combinational digital systems: Standard gate assembles, Binary adder, arithmetic functions, Decoder/De-multiplexer, Data selector/Multiplexer, Encoder. Sequential digital systems: A 1-bit memory, Flip-flops, shift registers, Ripple (Asynchronous) counters, Synchronous counters, Application of counters.

#### **TEXT BOOKS**

- [1]. Milliman. J, Halkias. C and Parikh. C.D., "Integrated Electronics", Tata Mc. Graw Hills 2<sup>nd</sup> Ed. 2010.

- [2]. R.L Boylestad and L. Nashelsky, "Electronic Devices & Circuit Theory:, Pearson Education.

- [3]. M. Morris Mano, "Digital Design", PHI Publishers.

#### **REFERENCE BOOKS**

- [1]. Mohammad Rashid, "Electronic Devices and Circuits", Cengage Learning Publishers.

- [2]. Sergio Fransco, "Design with Operational Amplifiers& Analog Integrated Circuits", TMH Publishers.

- [3]. Charles H.Roth, "Fundamentals of Logic Design", Cengage Learning Publishers

# Contents

- Introduction to ANALOG AND DIGITAL ELECTRONICS CIRCUITS.

- ► Fundamentals of BJT

### Introduction:

# What is Electronics?

- It is the branch of science and Technology which deals with the motion of electrons in various systems or devices.

- Electronics includes devices like diodes,transistors,rectifiers,etc.by these devices many systems work efficiently.

- The world is amazing by these very very tiny components which are embedded in to the systems(like radios,computers,etc.) for their working.

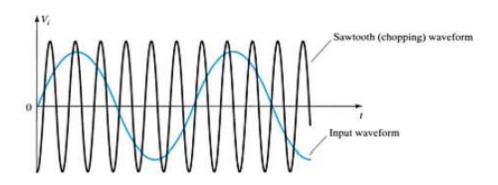

- ▶ Analog Electronics are electronics system with a continuously varying signal.

- ▶ Digital Electronics are electronics that handle digital signal.

| Factors           | Analog                                                    | Digital                                                                                     |  |

|-------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------|--|

| Waves             | Denoted by Sine waves                                     | Denoted by Square waves                                                                     |  |

| Signal            | Continuous signal representing physical measurements      | Discrete signal representing<br>discrete time signals<br>generated by digital<br>modulation |  |

| Data Transmission | Subject to deterioration by noise                         | Noise-immune without deterioration                                                          |  |

| Bandwidth         | Consumes less bandwidth                                   | Consumes more bandwidth                                                                     |  |

| Memory            | Stored in the form of wave signal                         | Stored in the form of binary bit                                                            |  |

| Power             | Draws large power                                         | Draws negligible power                                                                      |  |

| Impedance         | Low impedance                                             | High order of 100 megaohm                                                                   |  |

| Errors            | Analog instruments have considerable observational errors | Digital instruments are free from observational errors                                      |  |

### **Fundamentals of BJT:**

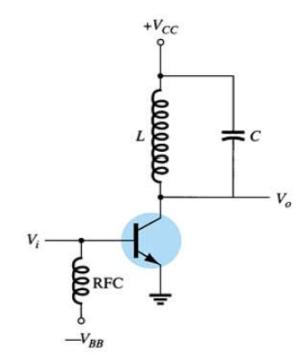

- Few most important applications of transistor are: as an amplifier, as an oscillator and as a switch.

- ▶ BJT is bipolar because both holes (+) and electrons (-) will take part in the current flow through the device

- N-type regions contains free electrons (negative carriers)

- P-type regions contains free holes (positive carriers)

- From the physical structure, BJTs can be divided into two groups: *npn* and *pnp* transistors.

# **Transistor Structure**

- In diodes there is one p-n junction.

- In Bipolar junction transistors (BJT), there are three layers and two p-n junctions.

Note: Arrow Direction from P to N (Like Diode)

## BASIC OPERATION OF TRANSISTOR

There are three mode of operations:

| Bias Mode       | E-B Junction    | C-B Junction |  |

|-----------------|-----------------|--------------|--|

| Saturation      | Forward         | Forward      |  |

| Active          | Forward Reverse |              |  |

| Inverted active | Reverse         | Forward      |  |

| Cutoff Reverse  |                 | Reverse      |  |

- If transistor is operating active mode, it can be used as amplifier.

- The transistor can be used as logical switch if it operates in cut-off and saturation mode.

# **Transistor Configuration:**

- Depending upon the terminals which are used as a common terminal to the input and output terminals, the transistors can be connected in the following three different configuration.

- 1. common base configuration

- 2. common emitter configuration

- 3. common collector configuration

| Basic circuit       | Common emitter  | Common collector | Common base      |

|---------------------|-----------------|------------------|------------------|

|                     | v <sub>o</sub>  | vo               |                  |

| Voltage gain        | high            | less than unity  | high, same as CE |

| Current gain        | high            | high             | less than unity  |

| Power gain          | high            | moderate         | moderate         |

| Phase inversion     | yes             | no               | no               |

| Input<br>impedance  | moderate ≈ 1 k  | highest ≈ 300 k  | low ≈ 50 Ω       |

| Output<br>impedance | moderate ≈ 50 k | low ≈ 300 Ω      | highest ≈ 1 Meg  |

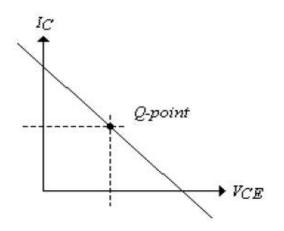

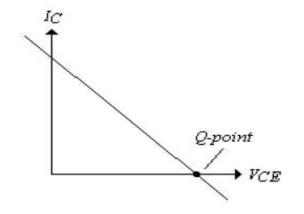

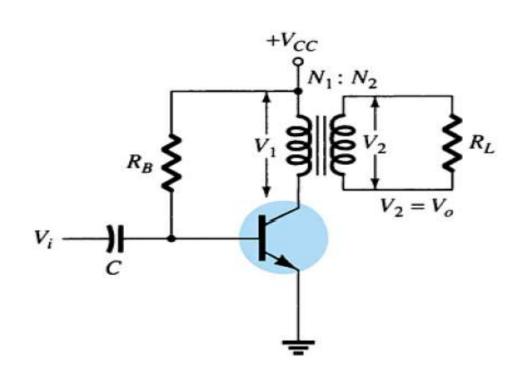

# Load Line and Q-point:

### Load Line:

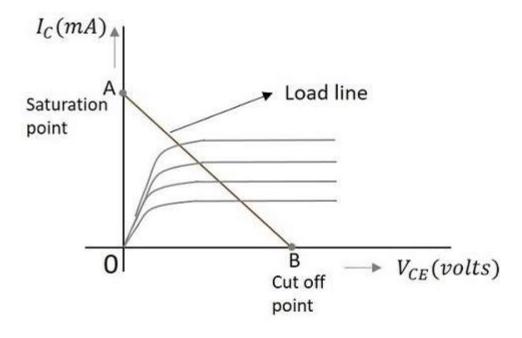

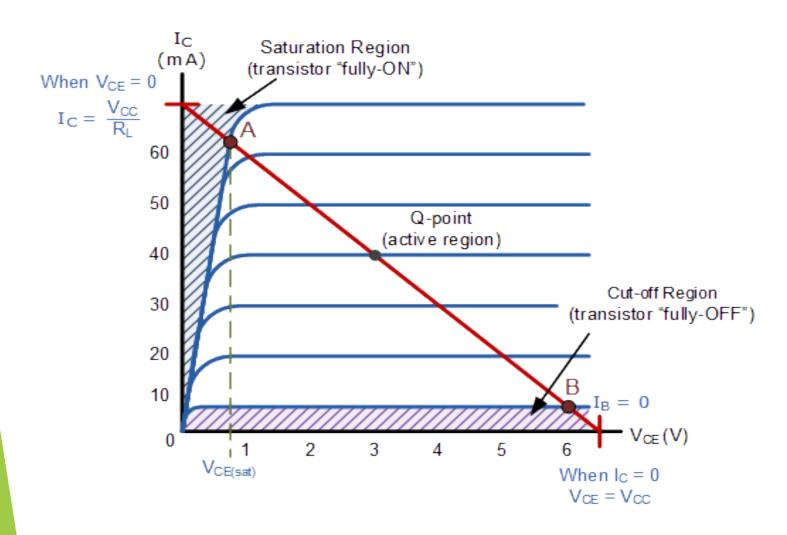

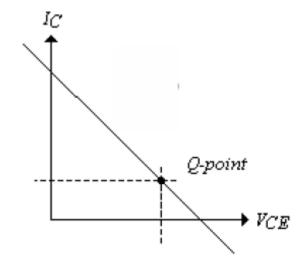

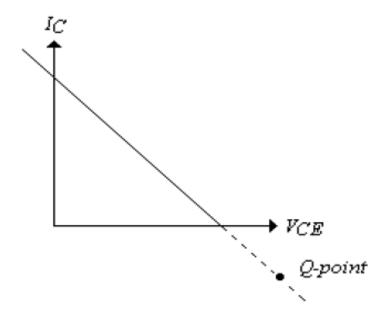

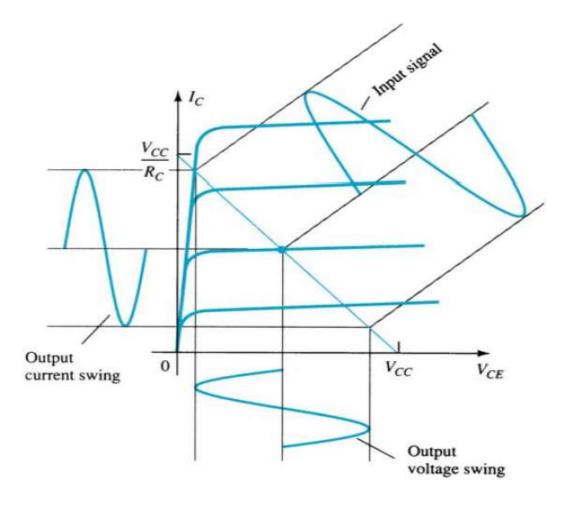

When a value for the maximum possible collector current is considered, that point will be present on the Y-axis, which is nothing but the **Saturation point**. As well, when a value for the maximum possible collector emitter voltage is considered, that point will be present on the X-axis, which is the **Cutoff point**. When a line is drawn joining these two points, such a line can be called as **Load line**.

This is called so as it symbolizes the output at the load. This line, when drawn over the output characteristic curve, makes contact at a point called as **Operating** point or quiescent point or simply **Q-point**.

### DC Load Line

When the transistor is given the bias and no signal is applied at its input, the load line drawn under such conditions, can be understood as **DC** condition. Here there will be no amplification as the **signal is absent**.

### **Q-Point (Static Operation Point)**

- When a line is drawn joining the saturation and cut off points, such a line can be called as Load line. This line, when drawn over the output characteristic curve, makes contact at a point called as Operating point.

- ► This operating point is also called as **quiescent point** or simply **Q-point**. There can be many such intersecting points, but the Q-point is selected in such a way that irrespective of AC signal swing, the transistor remains in the active region.

- ► The operating point should not get disturbed as it should remain stable to achieve faithful amplification. Hence the quiescent point or Q-point is the value where the Faithful Amplification is achieved.

# **Applications of BJT**

- Discrete-circuit design.

- Analog circuits.

- High frequency application such as radio frequency analog circuit.

- Digital circuits.

- Bi-CMOS (Bipolar+CMOS) circuits that combines the advantages of MOSFET and bipolar transistors.

- MOSFET: high-input impedance and low-power.

- Bipolar transistors: high-frequency-operation and highcurrent-driving capabilities.

Thank you.

# Contents of this class

- What is biasing circuit?

- Purpose of the DC biasing circuit

- Different Biasing circuits

- Fixed bias (base bias)

- Emitter bias

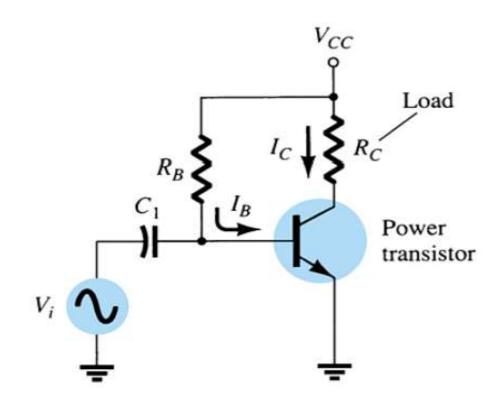

The analysis or design of any electronic amplifier therefore has two components: The dc portion and The ac portion

During the design stage, the choice of parameters for the required dc levels will affect the ac response.

### What is biasing circuit?

This process of selecting proper dc supply voltages and resistance for obtaining desired operating point or Q point is called as biasing and the ckt used for transistor biasing is called as biasing ckt.

- Purpose of the DC biasing circuit

- To turn the device "ON"

- To place it in operation in the region of its characteristic where the device operates most linearly, i.e. to set up the initial dc values of IB, IC, and VCE

- There are four conditions to be met by a transistor so that it acts as a faithful amplification:

- 1)Emitter base junction must be forward biased (VBE=0.7Vfor Si, 0.2V for Ge) and collector base junction must be reverse biased for all levels of i/p signal.

- 2) Vce voltage should not fall below VCE (sat) (0.3V for Si, 0.1V for Ge) for any part of the i/p signal. For VCE less than VCE (sat) the collector base junction is not probably reverse biased.

- 3) The value of the signal Ic when no signal is applied should be at least equal to the max. collector current due to signal alone.

- 4) Max. rating of the transistor Ic(max), VCE (max) and PD(max) should not be exceeded at any value of i/p signal.

- ▶ Even though the Q point is fixed properly, it is very important to ensure that the operating point remains stable where it is originally fixed. If the Q point shifted, the output voltage and current get clipped, thereby o/p signal is distorted.

- In practice, the Q-point tends to shift its position due to any or all of the following three main factors.

- 1) Reverse saturation current, Ico, which doubles for every 10oC raise in temperature

- 2) Base emitter Voltage ,VBE, which decreases by 2.5 mV per oC

- 3) Transistor current gain, hFE or B which increases with temperature.

### Important basic relationship

- $V_{BE} = 0.7V$

- $I_E = (\beta + 1) I_B \cong I_C$

- $I_C = \beta I_B$

### Different Biasing circuits:

- Fixed bias (base bias)

- Emitter bias

- Voltage divider bias(self bias)

- DC bias with voltage feedback

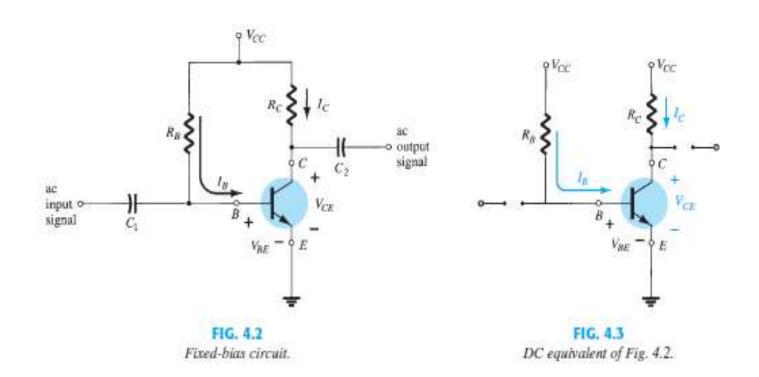

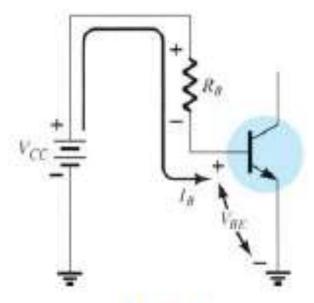

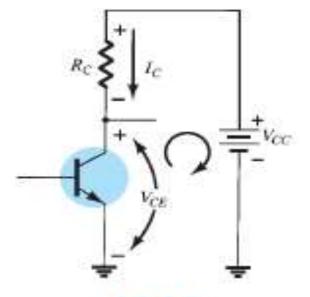

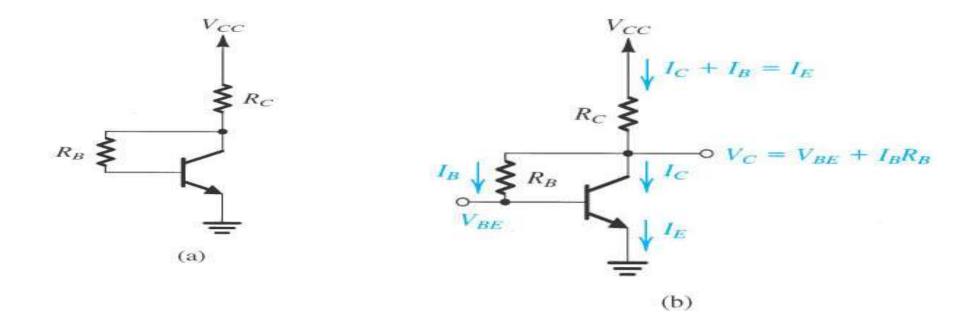

### 1)Fixed bias (base bias)

- The simplest transistor dc bias configuration.

- For dc analysis, open all the capacitance.

In the fig. shown, the single power source (for example, battery) is used for both collector and base of a transistor, although separate batteries can also be used.

FIG. 4.4

Base-emitter loop.

FIG. 4.5

Collector-emitter loop.

### **DC** Analysis

- Applying KVL to the input loop:  $+V_{CC} I_B R_B V_{BE} = 0$  $V_{CC} = I_B R_B + V_{BE}$

- From the above equation, deriving for IB, we get,

$$I_{B} = [V_{CC} - V_{BE}] / R_{B}$$

- The selection of R<sub>B</sub> sets the level of base current for the operating point.

- Applying KVL for the output loop:  $V_{CE} + I_C R_C V_{CC} = 0$

- $V_{CC} = I_{C}R_{C} + V_{CE}$

- Thus,

$$V_{CE} = V_{CC} - I_{CRC}$$

• In circuits where emitter is grounded,

$$V_{CE} = V_{E}$$

$$V_{BE} = V_B$$

### **Design and Analysis**

- Design: Given I<sub>B</sub>, I<sub>C</sub>, V<sub>CE</sub> and V<sub>CC</sub>, or I<sub>C</sub>, V<sub>CE</sub> and β, design the values of R<sub>B</sub>,

R<sub>C</sub> using the equations obtained by applying KVL to input and output loops.

- Analysis: Given the circuit values (V<sub>CC</sub>, R<sub>B</sub> and R<sub>C</sub>), determine the values of I<sub>B</sub>, I<sub>C</sub>

V<sub>CE</sub> using the equations obtained by applying KVL to input and output loops.

When the transistor is biased such that I<sub>B</sub> is very high so as to make I<sub>C</sub> very high such that I<sub>C</sub>R<sub>C</sub> drop is almost V<sub>CC</sub> and V<sub>CE</sub> is almost 0, the transistor is said to be in saturation.

$I_C$  sat =  $V_{CC} / R_C$  in a fixed bias circuit.

#### Verification

- Whenever a fixed bias circuit is analyzed, the value of  $I_{CQ}$  obtained could be verified with the value of  $I_{CSat}$  (=  $V_{CC}$  /  $R_C$ ) to understand whether the transistor is in active region.

- · In active region,

$$I_{CQ} = (I_{CSat}/2)$$

### Merits:

- It is simple to shift the operating point anywhere in the active region by merely changing the base resistor (RB).

- A very small number of components are required.

### **Demerits:**

- The collector current does not remain constant with variation in temperature or power supply voltage. Therefore the operating point is unstable.

- ▶ When the transistor is replaced with another one, considerable change in the value of B can be expected. Due to this change the operating point will shift.

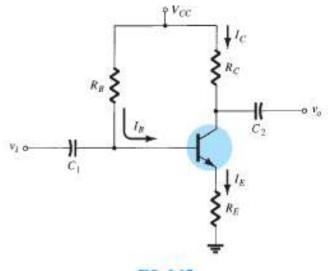

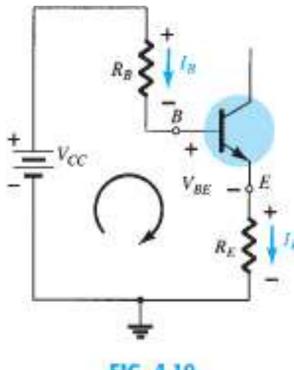

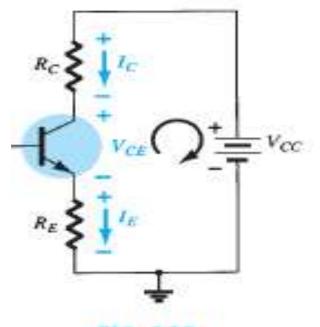

### Emitter Bias

- It can be shown that, including an emitter resistor in the fixed bias circuit improves the stability of Q point.

- Thus emitter bias is a biasing circuit very similar to fixed bias circuit with an emitter resistor added to it.

FIG. 4.17

BJT bias circuit with emitter resistor.

FIG. 4.18 DC equivalent of Fig. 4.17.

FIG. 4.19

Base-emitter loop.

FIG. 4.22

Collector-emitter loop.

· Writing KVL around the input loop we get,

$$V_{CC} = I_B R_B + V_{BE} + I_E R_E \qquad (1)$$

We know that,

$$I_E = (\beta + 1)I_B$$

(2)

Substituting this in (1), we get,

$$V_{CC} = I_B R_B + V_{BE} + (\beta + 1)I_B R_E$$

$$V_{CC}-V_{BE}=I_B(R_B+(\beta+1)~R_E)$$

Solving for IB:

$$I_B = (V_{CC} - V_{BE}) / [(R_B + (\beta+1) R_E)]$$

The expression for I<sub>B</sub> in a fixed bias circuit was,

$$I_B = (V_{CC} - V_{BE})/R_B$$

- $R_{EI}$  in the above circuit is  $(\beta+1)R_E$  which means that, the emitter resistance that is common to both the loops appears as such a high resistance in the input loop.

- Thus  $Ri = (\beta+1)R_E$  (more about this when we take up ac analysis)

### Collector - emitter loop

Applying KVL,

$$V_{CC} = I_{C}R_{C} + V_{CE} + I_{E}R_{E}$$

Ic is almost same as IE

Thus,

$$V_{CC} = I_C R_C + V_{CE} + I_C R_E$$

$$= I_C (R_C + R_E) + V_{CE}$$

$$V_{CE} = V_{CC} - I_C (R_C + R_E)$$

Since emitter is not connected directly to ground, it is at a potential V<sub>E</sub>, given by,

$$\begin{split} V_E &= I_E R_E \\ V_C &= V_{CE} + V_E \ \mathbf{OR} \ V_C = V_{CC} - I_C R_C \end{split}$$

Also,  $V_B = V_{CC} - I_B R_B \ \mathbf{OR} \ V_B = V_{BE} + V_E$

### Improved bias stability

- Addition of emitter resistance makes the dc bias currents and voltages remain closer to their set value even with variation in

- transistor beta

- temperature

### **Stability**

In a fixed bias circuit,  $I_B$  does not vary with  $\beta$  and therefore whenever there is an increase in  $\beta$ ,  $I_C$  increases proportionately, and thus  $V_{CE}$  reduces making the Q point to drift towards saturation.In an emitter bias circuit, As  $\beta$  increases,  $I_B$  reduces, maintaining almost same  $I_C$  and  $V_{CE}$  thus stabilizing the Q point against  $\beta$  variations.

### **Saturation current**

In saturation V<sub>CE</sub> is almost 0V, thus

$$V_{CC} = I_C (R_C + R_E)$$

Thus, saturation current

$$I_{C,sat} = V_{CC} / (R_C + R_E)$$

# Contents of this Class:

- ➤ Self-bias circuit

- ➤ Collector Feedback bias circuit

- ➤ Bias Stabilization

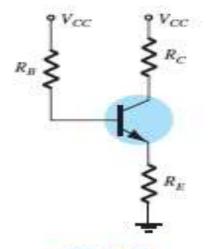

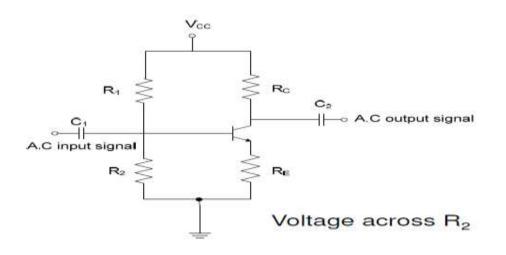

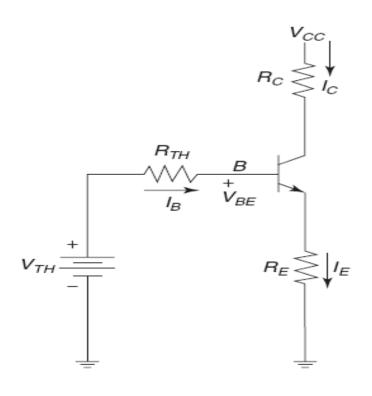

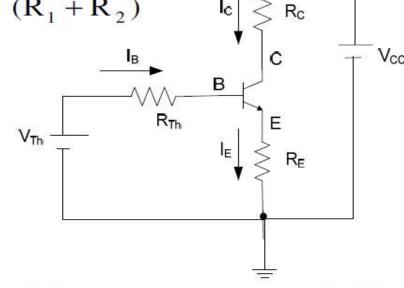

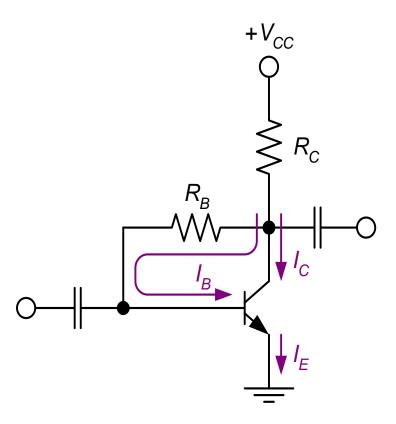

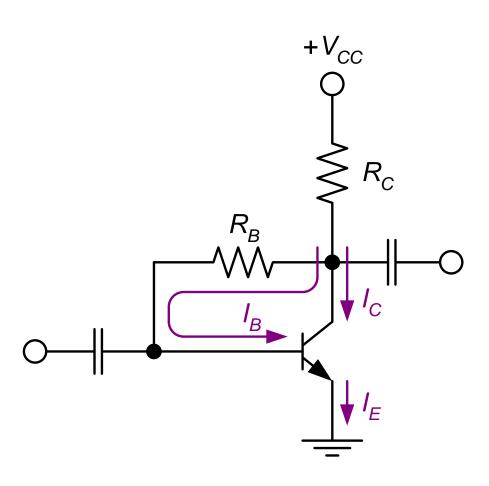

# Voltage divider bias (Self-bias circuit)

- This is the most widely used method to provide biasing and stabilization to a transistor.

- In this form of biasing, R<sub>1</sub> and R<sub>2</sub> divide the supply voltage V<sub>CC</sub> and voltage across R<sub>2</sub> provide fixed bias voltage V<sub>B</sub> at the transistor base.

- Also a resistance  $R_E$  is included in series with the emitter that provides the stabilization.

- The voltage divider as shown in the below figure is formed using external resistors R1 and R2. The voltage across R2 forward biases the emitter junction. By proper selection of resistors R1 and R2, the operating point of the transistor can be made independent of β. In this circuit, the voltage divider holds the base voltage fixed independent of base current provided the divider current is large compared to the base current. However, even with a fixed base voltage, collector current varies with temperature (for example) so an emitter resistor is added to stabilize the Q-point, similar to the above circuits with emitter resistor.

# Voltage divider bias (Self-bias circuit)

Voltage-divider bias circuit

Simplified voltage-divider circuit

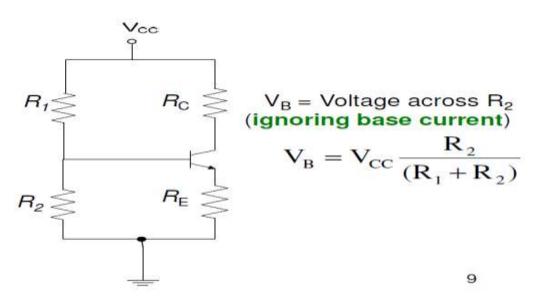

#### Voltage Divider Bias

$$V_{\text{B}} = V_{\text{Th}} = V_{\text{CC}} \frac{R_2}{(R_1 + R_2)} \qquad R_{\text{Th}} = R_1 \| R_2 = \frac{R_1 R_2}{(R_1 + R_2)} \qquad \text{Ic} \}$$

$$R_{Th} = R_1 || R_2 = \frac{R_1 R_2}{(R_1 + R_2)}$$

#### Base-Emitter Loop

$$V_{Th} - I_B R_{Th} - V_{BE} - (\beta + 1) I_B R_E = 0$$

or

$$I_A = \frac{V_{Th} - V_{BE}}{(\beta + 1)^2}$$

or,

$$I_B = \frac{V_{Th} - V_{BE}}{R_{Th} + (\beta + 1)R_E}$$

#### Collector- Emitter Loop

$$I_{C} = \beta I_{B} = \frac{\beta (V_{Th} - V_{BE})}{R_{Th} + (\beta + 1)R_{E}} \qquad V_{CE} = V_{CC} - I_{C}R_{C} - I_{E}R_{E} = V_{CC} - I_{C}R_{C} - (I_{C} + I_{B})R_{E}$$

For bais Stabilization:  $R_{Th} << (\beta+1)R_E$

$$I_{\rm C} \approx \frac{V_{\rm Th} - V_{\rm BE}}{R_{\rm E}}$$

#### Voltage divider bias (Self-bias circuit)

- Circuit recognition: The voltage divider in the base circuit.

- Advantages: The circuit Q-point values are stable against changes in  $h_{FE}$ .

- **Disadvantages:** Requires more components than most other biasing circuits.

- **Applications:** Used primarily to bias linear amplifier.

Load line equations:

Q-point equations (assume that  $h_{FE}R_E > 10R_2$ ):

$$I_{C(\text{sat})} = \frac{V_{CC}}{R_C + R_E}$$

$$V_{CE(\text{off})} = V_{CC}$$

$$\begin{aligned} V_B &= V_{CC} \, \frac{R_2}{R_1 + R_2} \\ V_E &= V_B - 0.7 \, \mathrm{V} \\ I_{CQ} &\cong I_E = \frac{V_E}{R_E} \\ V_{CEQ} &= V_{CC} - I_{CQ} \left( R_C + R_E \right) \end{aligned}$$

#### Voltage divider bias (Self-bias circuit)

#### Merits:

- Unlike above circuits, only one dc supply is necessary.

- Operating point is almost independent of  $\beta$  variation.

- Operating point stabilized against shift in temperature.

#### **Demerits:**

In this circuit, to keep IC independent of  $\beta$  the following condition must be

met:

$$I_C = \beta I_B = \beta \frac{\frac{V_{CC}}{1+R_1/R_2} - V_{be}}{(\beta+1)R_E + R_1 \parallel R_2} \approx \frac{\frac{V_{CC}}{1+R_1/R_2} - V_{be}}{R_E},$$

which is approximately the case if  $(\beta + 1)R_E >> R_1 \parallel R_2$

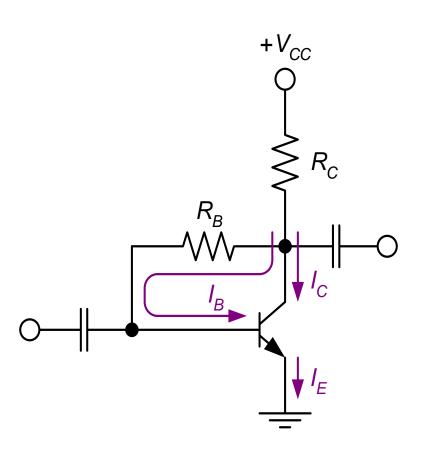

Circuit recognition: The base resistor is connected between the base and the collector terminals of the transistor.

**Advantage:** A simple circuit with relatively stable Q-point.

**Disadvantage:** Relatively poor ac characteristics.

**Applications:** Used primarily to bias linear amplifiers.

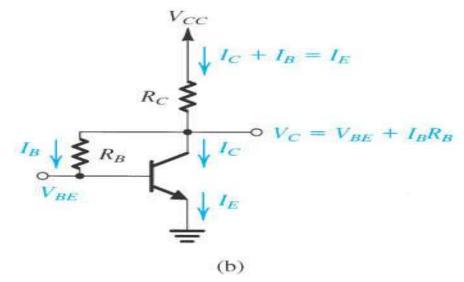

This configuration shown in figure employs negative feedback to prevent thermal runaway and stabilize the operating point. In this form of biasing, the base resistor RB is connected to the collector instead of connecting it to the DC source Vcc. So any thermal runaway will induce a voltage drop across the Rc resistor that will throttle the transistor's base current.

### R<sub>B</sub> provide <u>negative Feedback</u>

$$I_{E} = I_{C} + I_{B}$$

$V_{CC} = I_{E}R_{C} + I_{B}R_{B} + V_{BE}$

$I_{B} = \frac{I_{E}}{\beta + 1}$

$I_{E} = \frac{V_{CC} - V_{BE}}{R_{C} + \frac{R_{B}}{\beta + 1}}$

$V_{CC} >> V_{BE}$

$R_{C} >> \frac{R_{B}}{\beta + 1}$

$$V_{CC} = (I_C + I_B)R_C + I_BR_B + V_{BE}$$

$$I_B = \frac{V_{CC} - V_{BE}}{(h_{FE} + 1)R_C + R_B}$$

$$I_{CQ} = h_{FE}I_B$$

$$\begin{aligned} V_{CEQ} &= V_{CC} - \left(h_{FE} + 1\right) I_B R_C \\ &\cong V_{CC} - I_{CQ} R_C \end{aligned}$$

#### Q-point relationships:

$$I_{B} = \frac{V_{CC} - V_{BE}}{(h_{FE} + 1)R_{C} + R_{B}}$$

$$I_{CQ} = h_{FE}I_B$$

$$V_{CEQ} \cong V_{CC} - I_{CQ} R_C$$

#### **Merits:**

Circuit stabilizes the operating point against variations in temperature and  $\beta$  (i.e. replacement of transistor)

#### **Demerits:**

In this circuit, to keep Ic independent of  $\beta$ , the following condition must be met:

$$I_{\rm c} = \beta I_{\rm b} = \frac{\beta (V_{\rm cc} - V_{\rm be})}{R_{\rm b} + R_{\rm c} + \beta R_{\rm c}} \approx \frac{(V_{\rm cc} - V_{\rm be})}{R_{\rm c}}$$

which is the case when

$$\beta R_{\rm c} \gg R_{\rm b}$$

.

### Stabilization:

- Biasing refers to the application of D.C. voltages to setup the operating point in such a way that output signal is undistorted throughout the whole operation.

- Also once selected properly, the Q point should not shift because of change of Ic due to

- (i) variation due to replacement of the transistor of same type

- (ii) Temperature variation

#### **Stabilization:**

The process of making operating point independent of temperature changes or variation in transistor parameters is known as stabilization.

Stabilization of operating point is necessary due to

- Temperature dependence of Ic

- Individual variations

- Thermal runaway

Temperature dependence of Ic & Thermal runaway

$$I_C = \beta I_B + (\beta + 1)I_{CBO}$$

- IcBo is strong function of temperature. A rise of 10 oC doubles the IcBo and Ic will increase (β+1) times of IcBo

- The flow of Ic produce heat within the transistor and raises the transistor temperature further and therefore, further increase in IcBO

- This effect is cumulative and in few seconds, the Ic may become large enough to burn out the transistor.

- The self destruction of an unstablized transistor is known as thermal runaway.

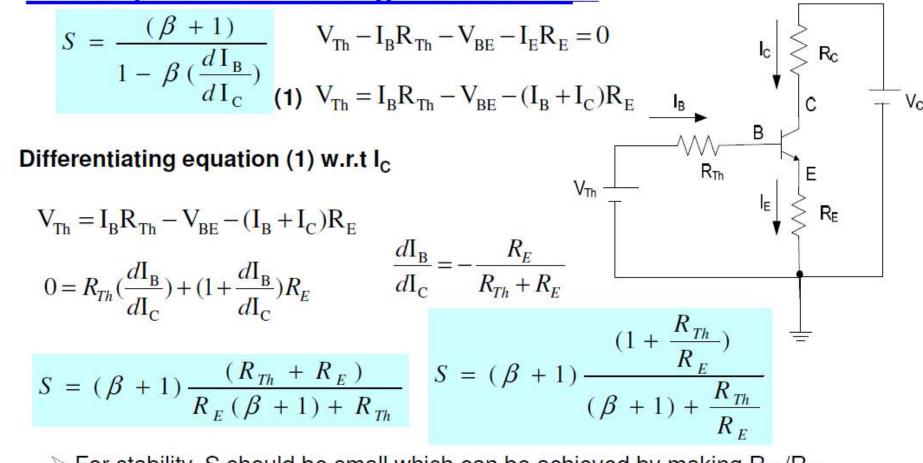

#### **Stability Factor:**

• The rate of change collector current Ic with respect to the collector leakage current IcBO at constant and IB is called stability factor, denoted by S.

$$I_C = \beta I_B + (\beta + 1)I_{CBO}$$

(1)

Differentiating equation (1) w.r.t l<sub>c</sub>

$$1 = \beta \left(\frac{dI_{B}}{dI_{C}}\right) + (\beta + 1)\frac{dI_{CBO}}{dI_{C}}$$

$$1 = \beta \left(\frac{dI_{B}}{dI_{C}}\right) + \frac{(\beta + 1)}{S}$$

$$1 = \beta \left(\frac{dI_{B}}{dI_{C}}\right) + (\beta + 1)\frac{dI_{CBO}}{dI_{C}}$$

$$1 = \beta \left(\frac{dI_{B}}{dI_{C}}\right) + \frac{(\beta + 1)}{S}$$

$$S = \frac{(\beta + 1)}{1 - \beta \left(\frac{dI_{B}}{dI_{C}}\right)}$$

$$1 - \beta \left(\frac{dI_{B}}{dI_{C}}\right)$$

• Stability Factor S':- The variation of  $I_C$  with  $V_{BE}$  is given by the stability factor S defined by the partial derivative:

$$S' \equiv \frac{\partial I_{C}}{\partial V_{BE}} \approx \frac{\Delta I_{C}}{\Delta V_{BE}}$$

**Stability Factor S":-** The variation of  $I_C$  with respect to  $\beta$  is represented by the stability factor, S", given as:

$$S'' \equiv \frac{\partial I_C}{\partial \beta} \approx \frac{\Delta I_C}{\Delta \beta}$$

#### Stability factor for Voltage Divider Bias

> For stability, S should be small which can be achieved by making  $R_{Th}/R_E$  small. For very small  $R_{Th}/R_E$ ; S = 1 (ideal case)

# Thank You.

#### Contents of the Class:

• Problems on fixed bias, emitter bias, voltage divider bias and collector feedback bias.

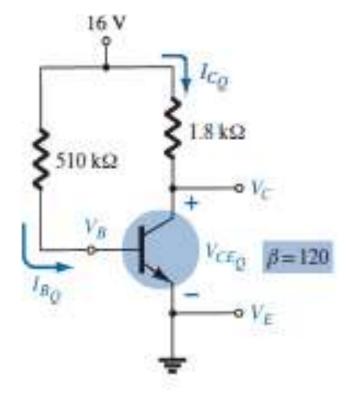

For the given fixed bias circuit determine

a. I<sub>EQ</sub>.

b. I<sub>CQ</sub>.

c. V<sub>CEQ</sub>.

d. V<sub>C</sub>.

e. V<sub>B</sub>.

f. V<sub>E</sub>.

(a)

$$I_{B_Q} = \frac{V_{CC} - V_{BE}}{R_B} = \frac{16 \text{ V} - 0.7 \text{ V}}{510 \text{ k}\Omega} = \frac{15.3 \text{ V}}{510 \text{ k}\Omega} = 30 \mu\text{A}$$

(b)

$$I_{C_Q} = \beta I_{B_Q} = (120)(30 \ \mu\text{A}) = 3.6 \ \text{mA}$$

(c)

$$V_{CE_Q} = V_{CC} - I_{C_Q} R_C = 16 \text{ V} - (3.6 \text{ mA})(1.8 \text{ k}\Omega) = 9.52 \text{ V}$$

(d)

$$V_C = V_{CE_Q} = 9.52V$$

(e)

$$V_B = V_{BE} = 0.7 \text{ V}$$

(f)

$$V_E = \mathbf{0} \mathbf{V}$$

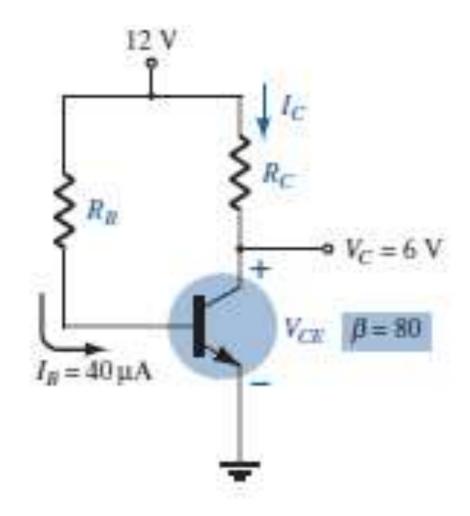

For the given circuits determine

- a. Ic

- b. Rc

- c. Rg.

- d. VCE

(a)

$$I_C = \beta I_B = 80(40 \ \mu\text{A}) = 3.2 \ \text{mA}$$

(b)

$$R_C = \frac{V_{R_C}}{I_C} = \frac{V_{CC} - V_C}{I_C} = \frac{12 \text{ V} - 6 \text{ V}}{3.2 \text{ mA}} = \frac{6 \text{ V}}{3.2 \text{ mA}} = 1.875 \text{ k}\Omega$$

(c)

$$R_B = \frac{V_{R_B}}{I_B} = \frac{12 \text{ V} - 0.7 \text{ V}}{40 \mu \text{A}} = \frac{11.3 \text{ V}}{40 \mu \text{A}} = 282.5 \text{ k}\Omega$$

(d)

$$V_{CE} = V_C = 6 \text{ V}$$

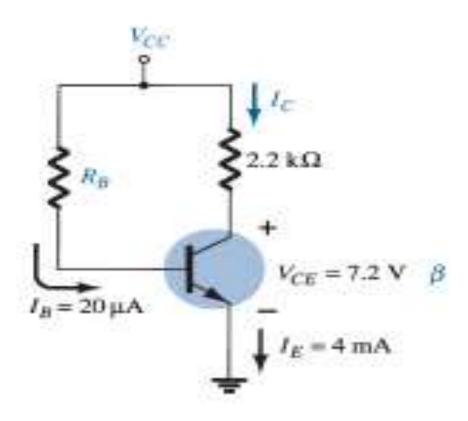

For the given circuits determine

(a)

$$I_C = I_E - I_B = 4 \text{ mA} - 20 \mu \text{A} = 3.98 \text{ mA} \approx 4 \text{ mA}$$

(b)

$$V_{CC} = V_{CE} + I_C R_C = 7.2 \text{ V} + (3.98 \text{ mA})(2.2 \text{ k}\Omega)$$

= **15.96 V**  $\cong$  16 V

(c)

$$\beta = \frac{I_C}{I_B} = \frac{3.98 \text{ mA}}{20 \mu\text{A}} = 199 \approx 200$$

(d)

$$R_B = \frac{V_{R_B}}{I_B} = \frac{V_{CC} - V_{BE}}{I_B} = \frac{15.96 \text{ V} - 0.7 \text{ V}}{20 \,\mu\text{A}} = 763 \text{ k}\Omega$$

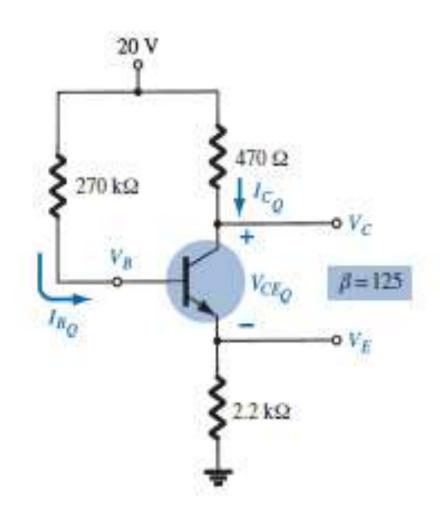

For emitter stabilized bias determines

(a)

$$I_{B_Q} = \frac{V_{CC} - V_{BE}}{R_B + (\beta + 1)R_E} = \frac{20 \text{ V} - 0.7 \text{ V}}{270 \text{ k}\Omega + (126)2.2 \text{ k}\Omega} = \frac{19.3 \text{ V}}{547.2 \text{ k}\Omega}$$

= 35.27  $\mu$ A

(b)

$$I_{C_o} = \beta I_{B_o} = (125)(35.27 \ \mu\text{A}) = 4.41 \ \text{mA}$$

(c)

$$V_{CE_Q} = V_{CC} - I_C(R_C + R_E) = 20 \text{ V} - (4.41 \text{ mA})(470 \text{ k}\Omega + 2.2 \text{ k}\Omega)$$

= 20 V - 11.77 V

= **8.23 V**

(d)

$$V_C = V_{CC} - I_C R_C = 20 \text{ V} - (4.41 \text{ mA})(470 \text{ k}\Omega) = 20 \text{ V} - 2.07 \text{ V}$$

= 17.93 V

(e)

$$V_B = V_{CC} - I_B R_B = 20 \text{ V} - (35.27 \ \mu\text{A})(270 \text{ k}\Omega)$$

= 20 V - 9.52 V = **10.48 V**

(f)

$$V_E = V_C - V_{CE} = 17.93 \text{ V} - 8.23 \text{ V} = 9.7 \text{ V}$$

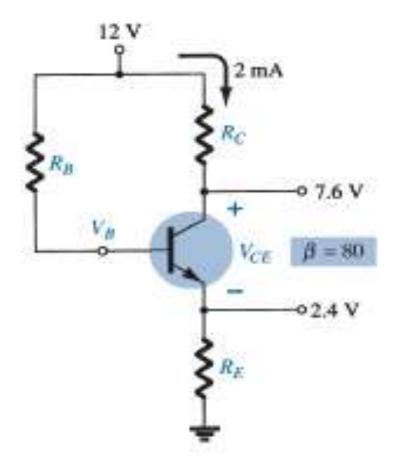

For the given circuit determines

- a. Rc.

- b. RE.

- c. Rg

- d. VCE

- e. VB.

(a)

$$R_C = \frac{V_{CC} - V_C}{I_C} = \frac{12 \text{ V} - 7.6 \text{ V}}{2 \text{ mA}} = \frac{4.4 \text{ V}}{2 \text{ mA}} = 2.2 \text{ k}\Omega$$

(b)

$$I_E \cong I_C$$

:  $R_E = \frac{V_E}{I_E} = \frac{2.4 \text{ V}}{2 \text{ mA}} = 1.2 \text{ k}\Omega$

(c)

$$R_B = \frac{V_{R_B}}{I_B} = \frac{V_{CC} - V_{BE} - V_E}{I_B} = \frac{12 \text{ V} - 0.7 \text{ V} - 2.4 \text{ V}}{2 \text{ mA/80}} = \frac{8.9 \text{ V}}{25 \mu\text{A}} = 356 \text{ k}\Omega$$

(d)

$$V_{CE} = V_C - V_E = 7.6 \text{ V} - 2.4 \text{ V} = 5.2 \text{ V}$$

(e)

$$V_B = V_{BE} + V_E = 0.7 \text{ V} + 2.4 \text{ V} = 3.1 \text{ V}$$

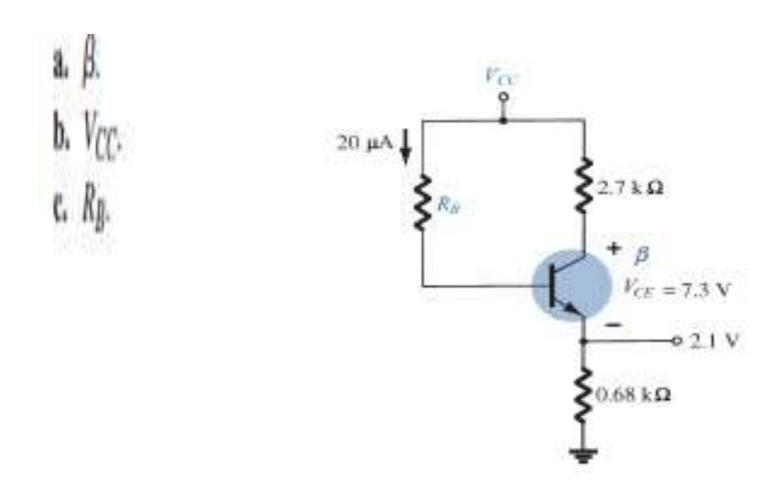

For the given circuit determines

(a)

$$I_C \cong I_E = \frac{V_E}{R_E} = \frac{2.1 \text{ V}}{0.68 \text{ k}\Omega} = 3.09 \text{ mA}$$

$$\beta = \frac{I_C}{I_B} = \frac{3.09 \text{ mA}}{20 \mu \text{A}} = 154.5$$

(b)

$$V_{CC} = V_{R_C} + V_{CE} + V_E$$

=  $(3.09 \text{ mA})(2.7 \text{ k}\Omega) + 7.3 \text{ V} + 2.1 \text{ V} = 8.34 \text{ V} + 7.3 \text{ V} + 2.1 \text{ V}$

=  $17.74 \text{ V}$

(c)

$$R_B = \frac{V_{R_B}}{I_B} = \frac{V_{CC} - V_{BE} - V_E}{I_B} = \frac{17.74 \text{ V} - 0.7 \text{ V} - 2.1 \text{ V}}{20 \mu\text{A}}$$

=  $\frac{14.94 \text{ V}}{20 \mu\text{A}} = 747 \text{ k}\Omega$

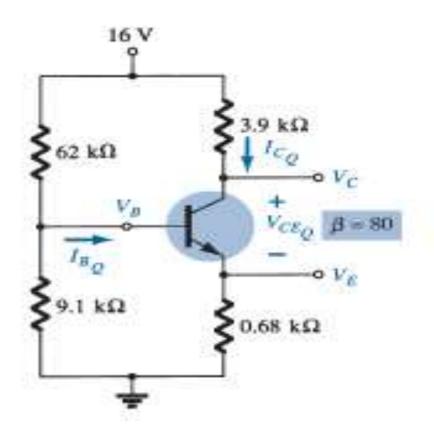

For the given voltage divider bias circuit determines

$$\beta R_E \ge 10R_2$$

(80)(0.68 k $\Omega$ )  $\ge 10(9.1 k $\Omega$ )

54.4 k $\Omega \ge 91 k\Omega$  (No!)$

(a) Use exact approach:

$$R_{Th} = R_1 || R_2 = 62 \text{ k}\Omega || 9.1 \text{ k}\Omega = 7.94 \text{ k}\Omega$$

$$E_{Th} = \frac{R_2 V_{CC}}{R_2 + R_1} = \frac{(9.1 \text{ k}\Omega)(16 \text{ V})}{9.1 \text{ k}\Omega + 62 \text{ k}\Omega} = 2.05 \text{ V}$$

$$I_{B_Q} = \frac{E_{Th} - V_{BE}}{R_{Th} + (\beta + 1)R_E} = \frac{2.05 \text{ V} - 0.7 \text{ V}}{7.94 \text{ k}\Omega + (81)(0.68 \text{ k}\Omega)}$$

$$= 21.42 \mu\text{A}$$

- (b)  $I_{C_O} = \beta I_{B_O} = (80)(21.42 \ \mu\text{A}) = 1.71 \ \text{mA}$

- (c)  $V_{CE_Q} = V_{CC} I_{C_Q} (R_C + R_E)$ = 16 V - (1.71 mA)(3.9 k $\Omega$  + 0.68 k $\Omega$ ) = **8.17 V**

- (d)  $V_C = V_{CC} I_C R_C$ = 16 V - (1.71 mA)(3.9 k $\Omega$ ) = 9.33 V

- (e)  $V_E = I_E R_E \cong I_C R_E = (1.71 \text{ mA})(0.68 \text{ k}\Omega)$ = **1.16 V**

- (f)  $V_B = V_E + V_{BE} = 1.16 \text{ V} + 0.7 \text{ V} = 1.86 \text{ V}$

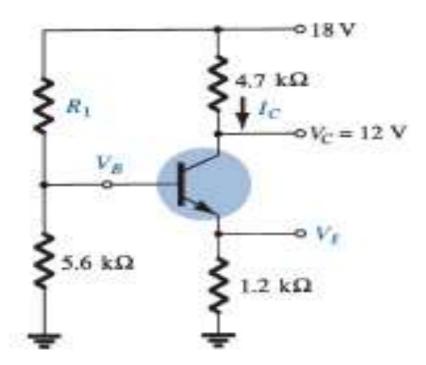

For the given voltage divider bias circuit determines

- I<sub>C</sub>.

- b.  $V_E$

- c.  $V_B$ .

- d. R<sub>1</sub>.

(a)

$$I_C = \frac{V_{CC} - V_C}{R_C} = \frac{18 \text{ V} - 12 \text{ V}}{4.7 \text{ k}\Omega} = 1.28 \text{ mA}$$

(b)

$$V_E = I_E R_E \cong I_C R_E = (1.28 \text{ mA})(1.2 \text{ k}\Omega) = 1.54 \text{ V}$$

(c)

$$V_B = V_{BE} + V_E = 0.7 \text{ V} + 1.54 \text{ V} = 2.24 \text{ V}$$

(d)

$$R_1 = \frac{V_{R_1}}{I_{R_1}}$$

:  $V_{R_1} = V_{CC} - V_B = 18 \text{ V} - 2.24 \text{ V} = 15.76 \text{ V}$

$$I_{R_1} \cong I_{R_2} = \frac{V_B}{R_2} = \frac{2.24 \text{ V}}{5.6 \text{ k}\Omega} = 0.4 \text{ mA}$$

$$R_1 = \frac{V_{R_1}}{I_{R_1}} = \frac{15.76 \text{ V}}{0.4 \text{ mA}} = 39.4 \text{ k}\Omega$$

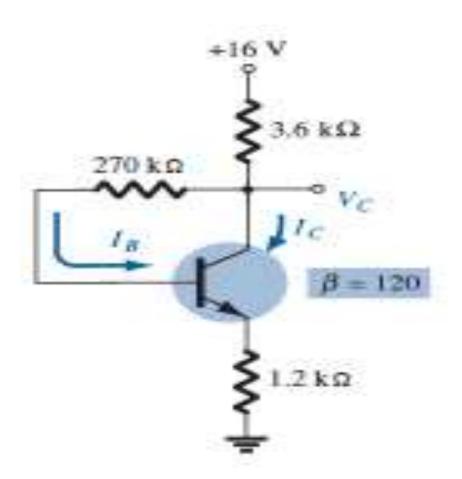

For the given collector feedback bias circuit determines

- a. Ig.

- b. I<sub>C</sub>

- c. V<sub>0</sub>

(a)

$$I_B = \frac{V_{CC} - V_{BE}}{R_B + \beta (R_C + R_E)} = \frac{16 \text{ V} - 0.7 \text{ V}}{270 \text{ k}\Omega + (120)(3.6 \text{ k}\Omega + 1.2 \text{ k}\Omega)}$$

= 18.09  $\mu$ A

(b)

$$I_C = \beta I_B = (120)(18.09 \ \mu\text{A})$$

= **2.17 mA**

(c)

$$V_C = V_{CC} - I_C R_C$$

= 16 V - (2.17 mA)(3.6 k $\Omega$ )

= **8.19 V**

# Thank You

#### Contents of the Class:

- AC analysis of Transistor

- Transistor Hybrid Model

- *h* parameters

- Analysis of the transistor amplifier using *h*-parameter.

# BJT Transistor modelling: (ac analysis of BJT)

- A model is an equivalent circuit that represents the AC characteristics of the transistor.

- A model uses circuit elements that approximate the behavior of the transistor.

- There are 2 models commonly used in small signal AC analysis of a transistor:

- i.  $r_e$  model

- ii. Hybrid equivalent model

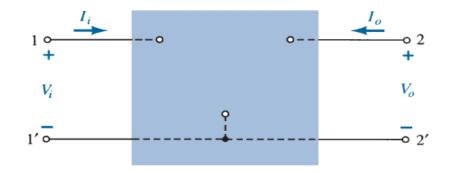

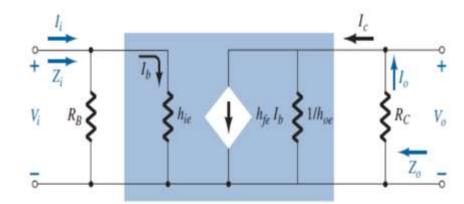

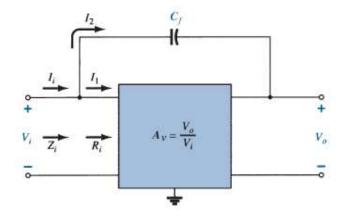

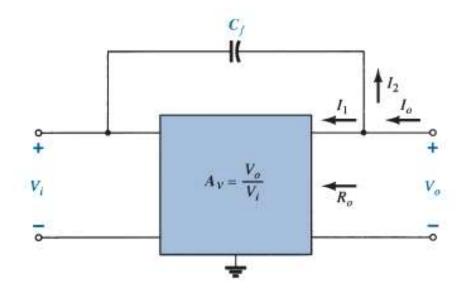

#### Two port device and hybrid model:

- For the hybrid equivalent model, the parameters are defined at an operating point.

- The quantities  $h_{ie}$ ,  $h_{re}$ ,  $h_{fe}$ , and  $h_{oe}$  are called hybrid parameters and are the components of a small signal equivalent circuit.

- The description of the hybrid equivalent model will begin with the general two port system.

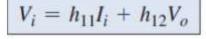

$$V_i = h_{11}I_i + h_{12}V_o$$

$$I_o = h_{21}I_i + h_{22}V_o$$

Two port System

The parameters relating the four variables are called *h-parameters*, from the word "hybrid." The term *hybrid* was chosen because the mixture of variables (V and I) in each equation results in a "hybrid" set of units of measurement for the hparameters.

- The four variables  $h_{11}$ ,  $h_{12}$ ,  $h_{21}$  and  $h_{22}$  are called hybrid parameters (the mixture of variables in each equation results in a "hybrid" set of units of measurement for the h parameters).

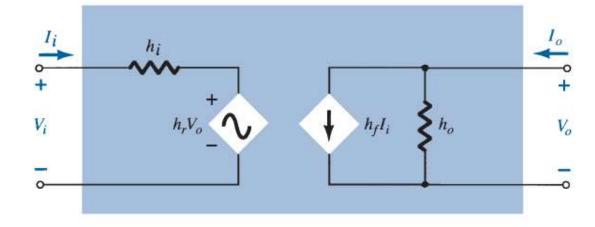

- $h_{11} = h_i$  (input resistance)= $V_i/I_i$  $\Big|_{V_o=0}$   $h_{12} = h_r$ (reversed voltage gain)= $V_i/V_o$  $\Big|_{I_i=0}$   $h_{21} = h_f$ (forward current gain)= $I_o/I_i$  $\Big|_{V_o=0}$   $h_{22} = h_o$ (output admittance)= $I_o/V_o$  $\Big|_{I_i=0}$

# Hybrid equivalent circuit:

$h_{11} \rightarrow i$ nput resistance  $\rightarrow h_i$   $h_{12} \rightarrow r$ everse transfer voltage ratio  $\rightarrow h_r$   $h_{21} \rightarrow f$ orward transfer current ratio  $\rightarrow h_f$  $h_{22} \rightarrow o$ utput conductance  $\rightarrow h_o$

$$I_o = h_{21}I_i + h_{22}V_o$$

Hybrid Equivalent Circuit

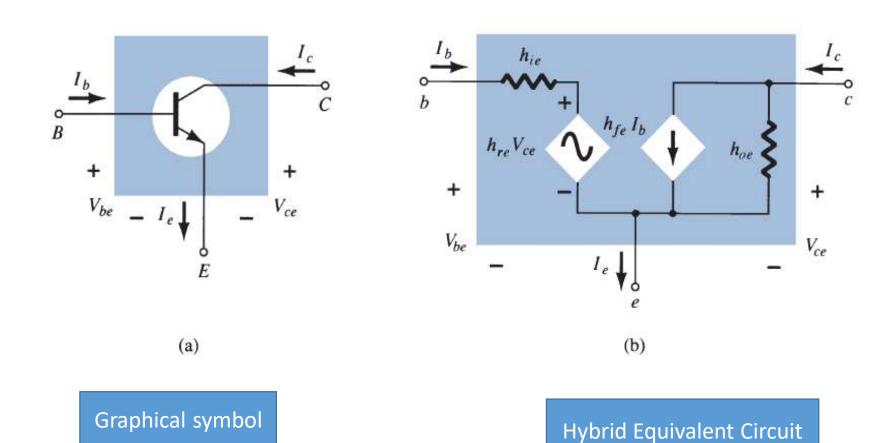

# Common Emitter Configuration:

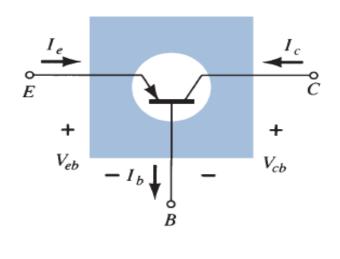

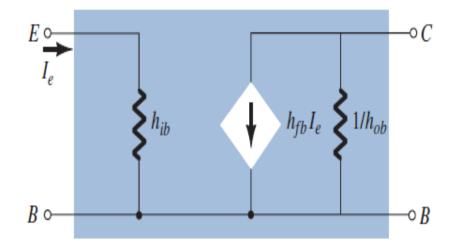

# Common Base Configuration:

(a)

**Graphical Symbol**

Hybrid Equivalent Circuit

- Essentially, the transistor model is a three terminal two port system.

- The h parameters, however, will change with each configuration.

- To distinguish which parameter has been used or which is available, a second subscript has been added to the h parameter notation.

- For the common base configuration, the lowercase letter b is added, and for common emitter and common collector configurations, the letters e and c are used respectively

| Configuration    | I,             | $I_o$          | Vi       | Vo       |

|------------------|----------------|----------------|----------|----------|

| Common emitter   | I <sub>b</sub> | I <sub>c</sub> | $V_{be}$ | $V_{ce}$ |

| Common base      | $I_e$          | $I_c$          | $V_{eb}$ | Vcb      |

| Common Collector | I <sub>b</sub> | $I_e$          | $V_{be}$ | $V_{ec}$ |

Input and output current and voltage of different transistor configuration in terms of h-parameter

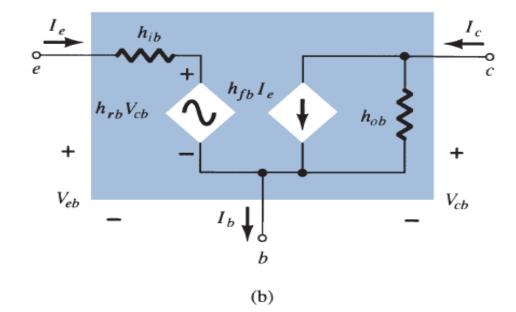

- Normally  $h_r$  is a relatively small quantity, its removal is approximated by  $h_r$  and  $h_rV_o = 0$ , resulting in a short circuit equivalent.

- The resistance determined by  $^1/h_0$  is often large enough to be ignored in comparison to a parallel load, permitting its replacement by an open circuit equivalent.

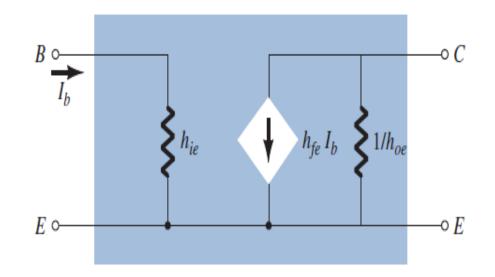

# Approximate Hybrid Equivalent Circuit:

Approximate Common Emitter

Hybrid Equivalent Circuit

Approximate Common Base Hybrid Equivalent Circuit

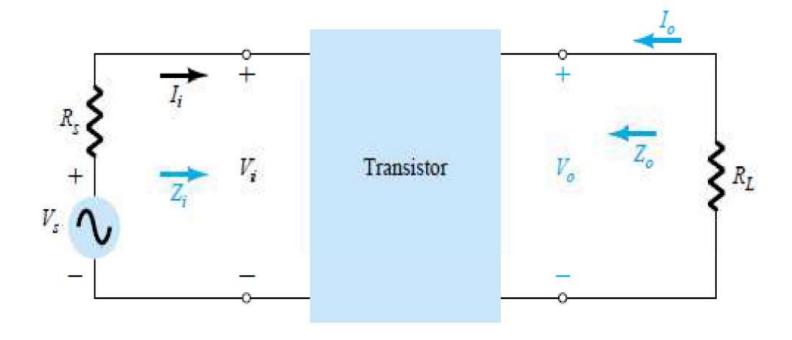

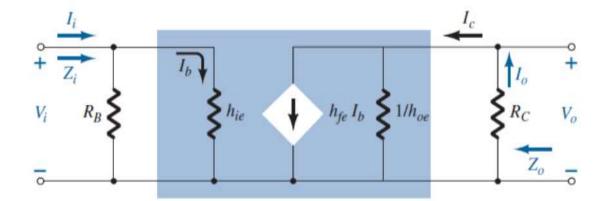

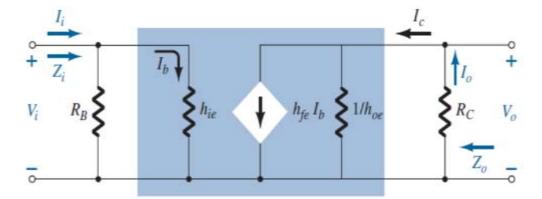

### Analysis of transistor amplifier using h-parameter:

Two-port system

### Analysis of transistor amplifier using h-parameter:

Substituting the complete hybrid equivalent circuit into the two-port system

### Analysis of transistor amplifier using h-parameter:

For analysis of transistor amplifier we have to determine the following terms:

- Current Gain $(A_i) = \frac{I_o}{I_i}$

- Voltage gain $(A_V) = \frac{V_o}{V_i}$

- Input impedance $(Z_i) = \frac{V_i}{I_i}$

- Output impedance $(Z_o) = \frac{V_o}{I_o}$

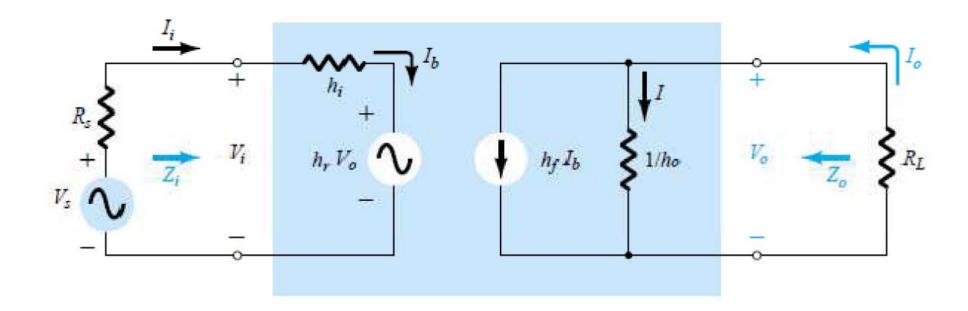

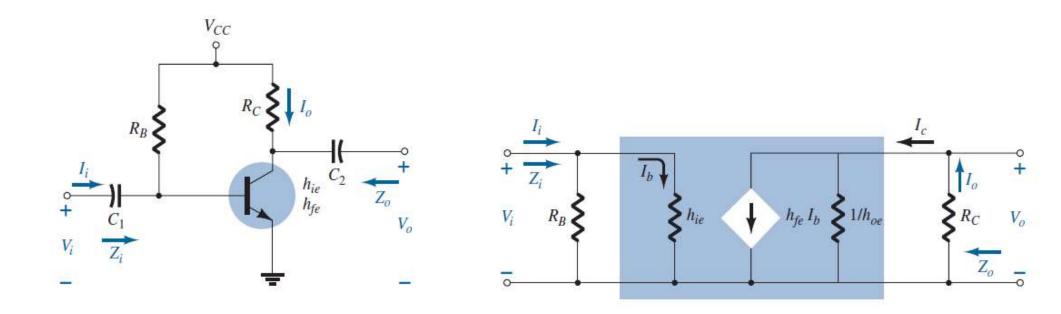

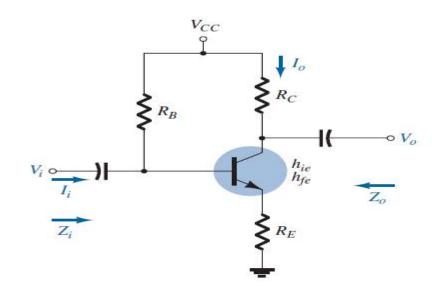

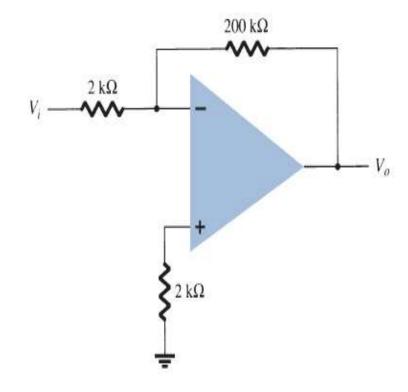

### Fixed-bias Configuration(ac analysis):

Fixed bias configuration

Substituting the approximate hybrid equivalent circuit into the ac equivalent network

**Z**<sub>i</sub> From Fig.

$$Z_i = R_B \| h_{ie}$$

**Z**<sub>o</sub> From Fig.

$$Z_o = R_C \|1/h_{oe}$$

$\mathbf{A_v}$  Using  $R' = 1/h_{oe} \| R_C$ , we obtain

$$V_o = -I_o R' = -I_C R'$$

$$= -h_{fe} I_b R'$$

$$V_i$$

and

75.5353

with

$$V_o = -h_{fe} \frac{V_i}{h_{ie}} R'$$

so that

$$A_{v} = \frac{V_{o}}{V_{i}} = -\frac{h_{ie}(R_{C} || 1/h_{oe})}{h_{ie}}$$

$$A_i = \frac{I_o}{I_i} \cong h_{fe}$$

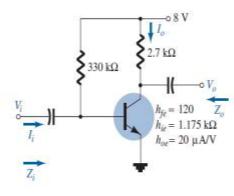

**EXAMPLE** For the network of Fig. determine:

- a.  $Z_i$ . b.  $Z_o$ .

- c. A<sub>y</sub>.

- d.  $A_i$ .

FIG. Example

#### Solution:

a.

$$Z_i = R_B || h_{ie} = 330 \text{ k}\Omega || 1.175 \text{ k}\Omega$$

$\approx h_{ie} = 1.171 \text{ k}\Omega$

b.

$$r_o = \frac{1}{h_{oe}} = \frac{1}{20 \,\mu\text{A/V}} = 50 \,\text{k}\Omega$$

$$Z_o = \frac{1}{h_{oe}} ||R_C = 50 \text{ k}\Omega|| 2.7 \text{ k}\Omega = 2.56 \text{ k}\Omega \approx R_C$$

c.

$$A_v = -\frac{h_{fe}(R_C \| 1/h_{oe})}{h_{ie}} = -\frac{(120)(2.7 \text{ k}\Omega \| 50 \text{ k}\Omega)}{1.171 \text{ k}\Omega} = -262.34$$

d.

$$A_i \cong h_{fe} = 120$$

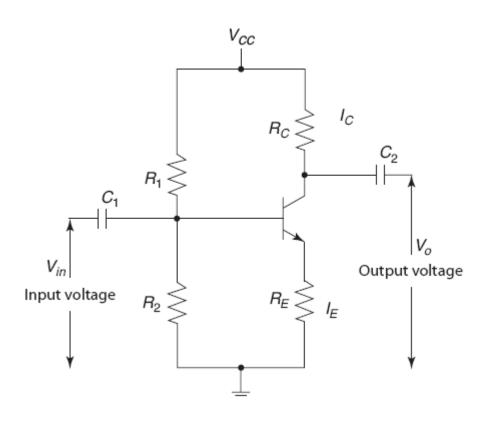

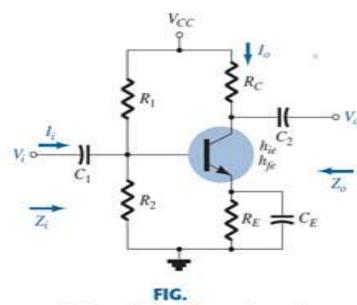

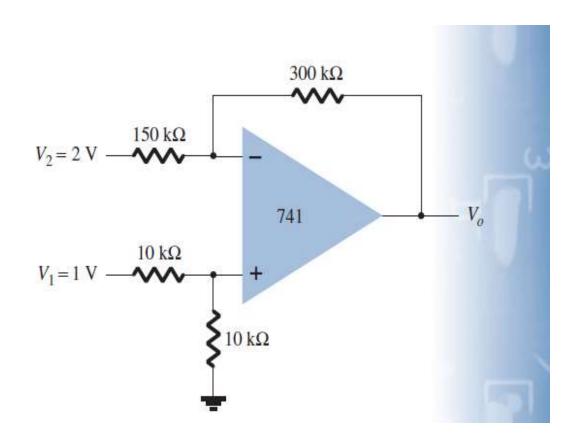

#### Voltage-divider bias:

For the voltage-divider bias configuration the resulting small-signal ac equivalent network will have the same as fixed bias circuit, with  $R_B$  replaced by  $R' = R_1 \| R_2$ .

Voltage-divider bias configuration.

#### Voltage-divider bias:

$\mathbf{Z}_{i}$  From Fig. with  $R_{B} = R'$ ,

$$Z_i = R_1 \| R_2 \| h_{ie}$$

**Z<sub>0</sub>** From Fig.

$$Z_o \cong R_C$$

$A_{V}$

$$A_{v} = -\frac{h_{fe}(R_{C} \| 1/h_{oe})}{h_{ie}}$$

$A_i$

$$A_i = \frac{h_{fe}(R_1 || R_2)}{R_1 || R_2 + h_{ie}}$$

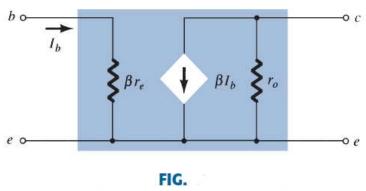

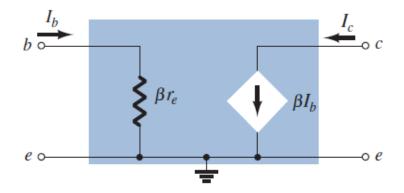

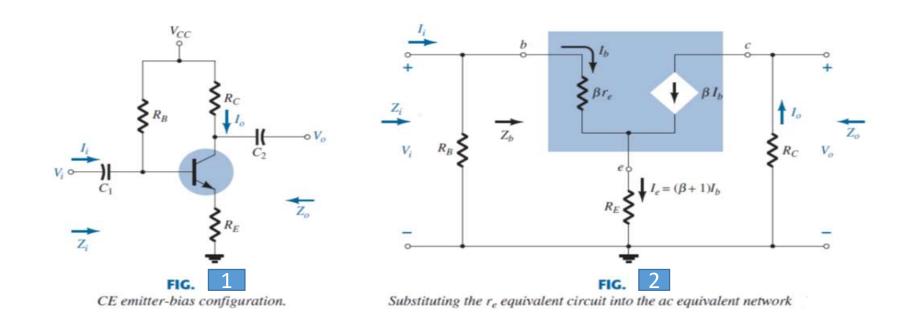

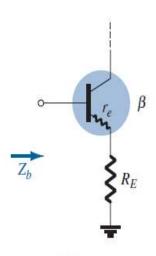

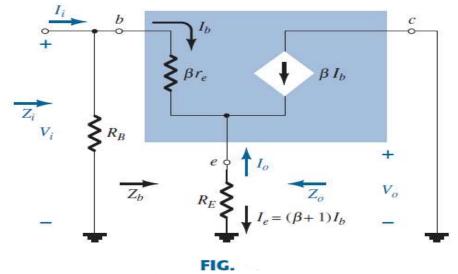

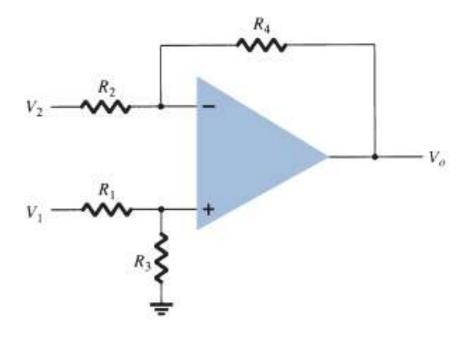

# CE emitter-bias Configuration using r<sub>e</sub> model:

$r_e$  model for the common-emitter transistor configuration including effects of  $r_o$ .

re model without effect of ro

# CE emitter-bias Configuration using r<sub>e</sub> model:

Applying Kirchhoff's voltage law to the input side of Fig. results in

$$V_i = I_b \beta r_e + I_e R_E$$

$$V_i = I_b \beta r_e + (\beta + I) I_b R_E$$

or

and the input impedance looking into the network to the right of  $R_B$  is

$$Z_b = \frac{V_i}{I_b} = \beta r_e + (\beta + 1)R_E$$

The result as displayed in Fig. 3 reveals that the input impedance of a transistor with an unbypassed resistor  $R_E$  is determined by

$$Z_b = \beta r_e + (\beta + 1)R_E$$

Because  $\beta$  is normally much greater than 1, the approximate equation is

$$Z_b \cong \beta r_e + \beta R_E$$

and

$$Z_b \cong \beta(r_e + R_E)$$

Because  $R_E$  is usually greater than  $r_e$ , Eq. can be further reduced to

$$Z_b \cong \beta R_E$$

we have

$$Z_i = R_B \| Z_b$$

Defining the input impedance of a transistor with an unbypassed emitter resistor.

**Z<sub>o</sub>** With  $V_i$  set to zero,  $I_b = 0$ , and  $\beta I_b$  can be replaced by an open-circuit equivalent. The result is

$$Z_o = R_C$$

Av

and  $I_b = \frac{V_i}{Z_b}$   $V_o = -I_o R_C = -\beta I_b R_C$   $= -\beta \left(\frac{V_i}{Z_b}\right) R_C$

with

$$A_{v} = \frac{V_{o}}{V_{i}} = -\frac{\beta R_{C}}{Z_{b}}$$

Substituting  $Z_b \cong \beta(r_e + R_E)$  gives

$$A_{v} = \frac{V_{o}}{V_{i}} \cong -\frac{R_{C}}{r_{e} + R_{E}}$$

and for the approximation  $Z_b \cong \beta R_E$ ,

$$A_{v} = \frac{V_{o}}{V_{i}} \cong -\frac{R_{C}}{R_{E}}$$

Note the absence of  $\beta$  from the equation for  $A_{\nu}$  demonstrating an independence in variation of  $\beta$ .

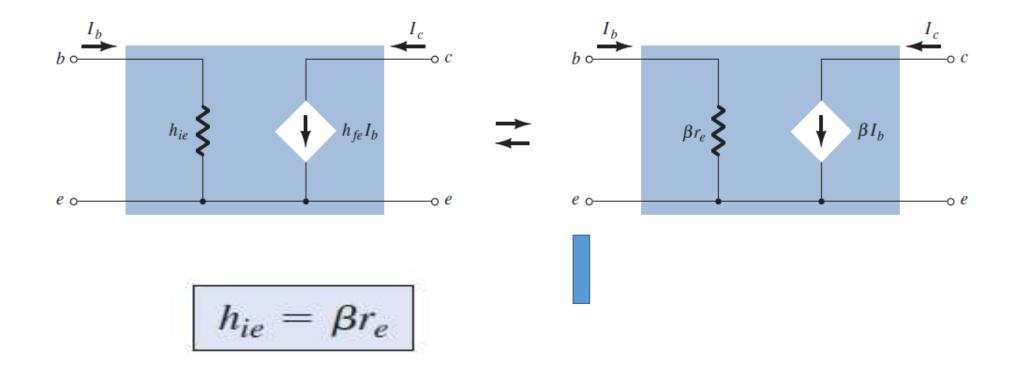

### Relationship between r<sub>e</sub> and hybrid model:

$$h_{fe} = \beta_{ac}$$

$r_o = \frac{1}{h_{oe}}$

### Unbypassed emitter-bias Configuration analysis using Hybrid model:

- For the CE unbypassed emitter-bias configuration, the small-signal ac model will be the same as  $r_e$  model analysis, with  $\beta r_e$  replaced by  $h_{ie}$  and  $\beta I_b$  by  $h_{fe}I_b$ .

- The analysis will proceed in the same manner as re model analysis.

CE unbypassed emitter-bias configuration.

### Unbypassed emitter-bias Configuration analysis using Hybrid model:

$Z_i$

and

Zo

Av

and

$Z_b \cong h_{fe}R_E$

$Z_i = R_B \| Z_b$

$Z_o = R_C$

$A_{v} = -\frac{h_{fe}R_{C}}{Z_{b}} \cong -\frac{h_{fe}R_{C}}{h_{fe}R_{E}}$

$A_{v} \simeq -\frac{R_{C}}{R_{E}}$

$A_i$

$A_i = -\frac{h_{fe}R_B}{R_B + Z_b}$

or

$$A_i = -A_v \frac{Z_i}{R_C}$$

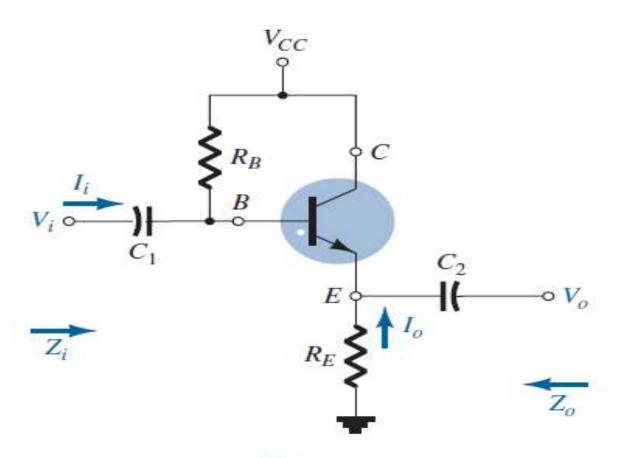

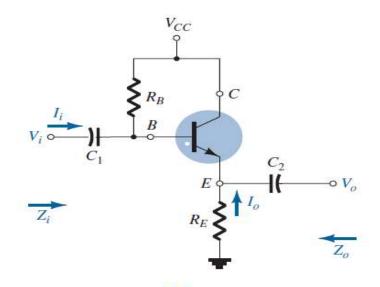

#### Emitter-follower Configuration(common-collector configuration):

- When the output is taken from the emitter terminal of the transistor as shown in figure, the network is referred to as an *emitter-follower*.

- The output voltage is always slightly less than the input signal due to the drop from base to emitter, but the approximation  $A_{\nu} \cong 1$  is usually a good one.

- The fact that  $V_o$  "follows" the magnitude of  $V_i$  with an in-phase relationship accounts for the terminology emitter-follower.

- The most common emitter-follower configuration appears in Fig. In fact, because the collector is grounded for ac analysis, it is actually a common-collector configuration.

- The emitter-follower configuration is frequently used for impedance-matching purposes.

- It presents a high impedance at the input and a low impedance at the output, which is the direct opposite of the standard fixed-bias configuration. The resulting effect is much the same as that obtained with a transformer, where a load is matched to the source impedance for maximum power transfer through the system.

FIG.

Emitter-follower configuration.

# Analysis of emitter follower using <u>re model</u>:

FIG.

Emitter-follower configuration.

Substituting the  $r_e$  equivalent circuit into the ac equivalent network of Fig.

**Z**<sub>i</sub> The input impedance is determined in the same manner as described in the preceding section:

$$Z_i = R_B \| Z_b$$

with

$$Z_b = \beta r_e + (\beta + 1)R_E$$

or

$$Z_b \cong \beta(r_e + R_E)$$

and

$$Z_b \cong \beta R_E$$

$R_E \gg r_e$

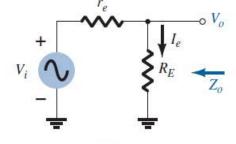

#### The output impedance is best described by first writing the equation for the current $I_b$ ,

$$I_b = \frac{V_i}{Z_b}$$

and then multiplying by  $(\beta + 1)$  to establish  $I_e$ . That is,

$$I_e = (\beta + 1)I_b = (\beta + 1)\frac{V_i}{Z_b}$$

Substituting for  $Z_b$  gives

$$I_e = \frac{(\beta + 1)V_i}{\beta r_e + (\beta + 1)R_E}$$

or

$$I_e = \frac{V_i}{[\beta r_e/(\beta + 1)] + R_E}$$

but

$$(\beta + 1) \cong \beta$$

and

$$\frac{\beta r_e}{\beta + 1} \cong \frac{\beta r_e}{\beta} = r_e$$

so that

$$I_e \simeq \frac{V_i}{r_e + R_E}$$

FIG.

Defining the output impedance for the emitter-follower configuration. If we now construct the network defined by Eq. results.

To determine  $Z_o$ ,  $V_i$  is set to zero and

$$Z_o = R_E || r_e$$

the configuration of Fig.

Because  $R_E$  is typically much greater than  $r_e$ , the following approximation is often applied:

$$Z_o \simeq r_e$$

$A_{\nu}$  Figure 38 can be used to determine the voltage gain through an application of the voltage-divider rule:

$$V_o = \frac{R_E V_i}{R_E + r_e}$$

and

$$A_{v} = \frac{V_{o}}{V_{i}} = \frac{R_{E}}{R_{E} + r_{e}}$$

Because  $R_E$  is usually much greater than  $r_e$ ,  $R_E + r_e \approx R_E$  and

$$A_{v} = \frac{V_{o}}{V_{i}} \cong 1$$

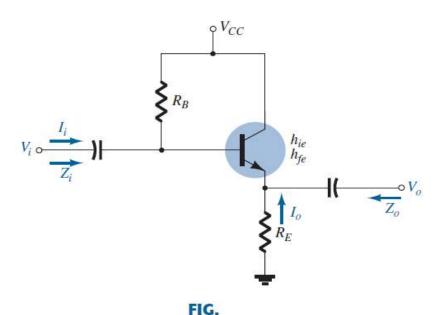

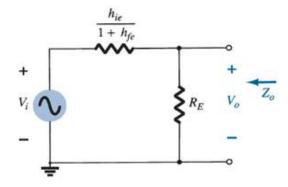

#### **Analysis of Emitter-follower Configuration using Hybrid Model:**

- For the emitter-follower, the small-signal ac model will be the same as  $r_e$  model analysis with  $\beta r_e = h_{ie}$  and  $\beta = h_{fe}$ .

- The analysis will proceed in the same manner as r<sub>e</sub> model analysis of emitter follower.

Emitter-follower configuration.

$$Z_b \cong h_{fe}R_E$$

$$Z_i = R_B \| Z_b$$

$Z_o$  For  $Z_o$ , the output network defined by the resulting equations will appear as shown in Fig.

$$Z_o = R_E \| \frac{h_{ie}}{1 + h_{fe}}$$

or, because  $1 + h_{fe} \cong h_{fe}$ ,

$$Z_o \cong R_E \| \frac{h_{ie}}{h_{fe}} \|$$

Defining  $Z_o$  for the emitter-follower configuration.

#### $A_{\nu}$ For the voltage gain, the voltage-divider rule can be applied

$$V_o = \frac{R_E(V_i)}{R_E + h_{ie}/(1 + h_{fe})}$$

but, since  $1 + h_{fe} \cong h_{fe}$ ,

$$A_{v} = rac{V_{o}}{V_{i}} \cong rac{R_{E}}{R_{E} + h_{ie}/h_{fe}}$$

Ai

$$A_i = \frac{h_{fe} R_B}{R_B + Z_b}$$

or

$$A_i = -A_v \frac{Z_i}{R_E}$$

#### Contents of the Class:

- Cascaded Systems

- Cascode Connection

- Darlington Connection

- Feedback pair

- hybrid pi model

- Junction Field Effect Transistors (JFETs)

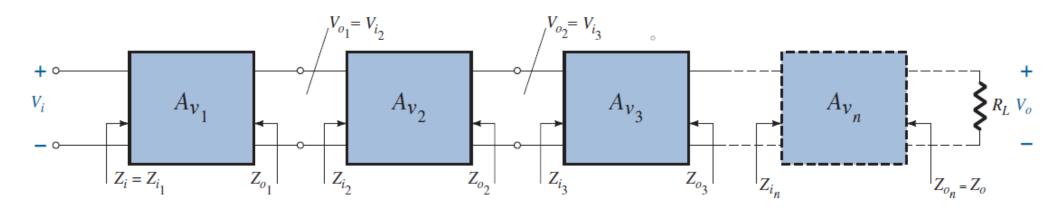

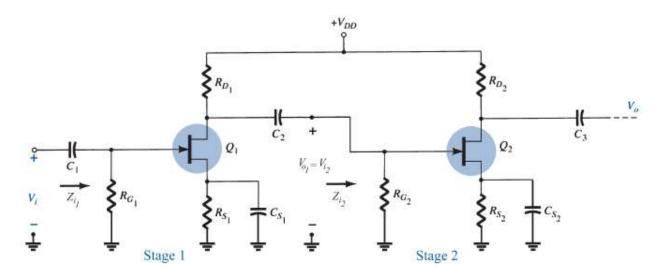

### **Cascaded Systems:**

•

**FIG.**Cascaded system.

#### Cascaded Systems:

• When two or more amplifier are cascaded such as that appearing where  $A_{\nu_1}, A_{\nu_2}, A_{\nu_3}$ , and so on, are the voltage gains of each stage

under loaded conditions. That is,  $A_{v_1}$  is determined with the input impedance to  $A_{v_2}$  acting as the load on  $A_{v_1}$ . For  $A_{v_2}$ ,  $A_{v_1}$  will determine the signal strength and source impedance at the input to  $A_{v_2}$ . The total gain of the system is then determined by the product of the individual gains as follows:

$$A_{\nu_T} = A_{\nu_1} \cdot A_{\nu_2} \cdot A_{\nu_3} \cdot \cdots$$

and the total current gain is given by

$$A_{i_T} = -A_{v_T} \frac{Z_{i_1}}{R_L}$$

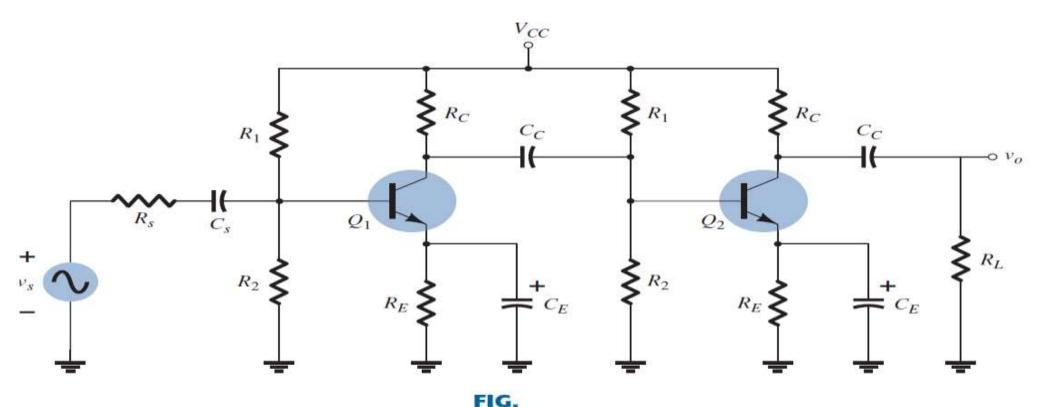

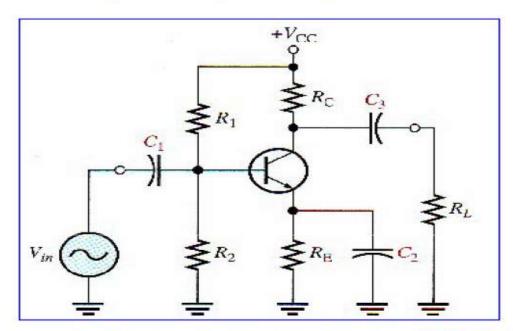

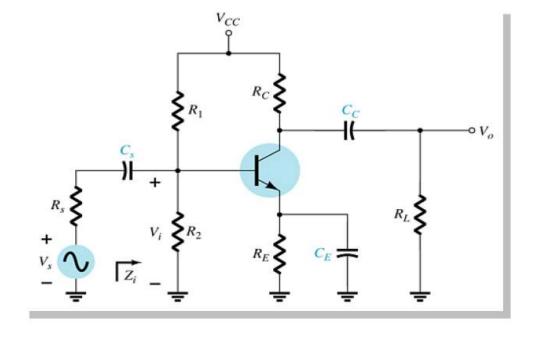

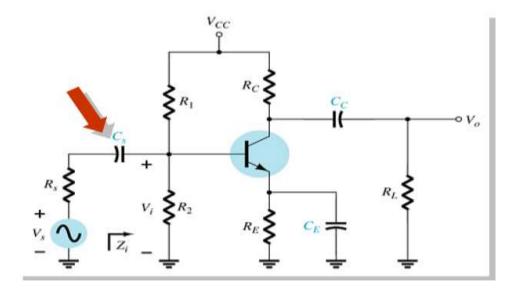

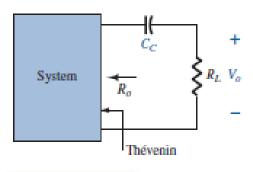

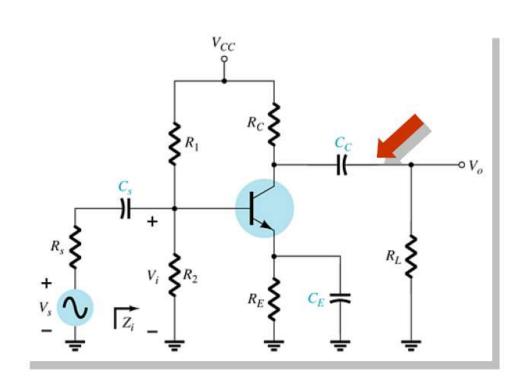

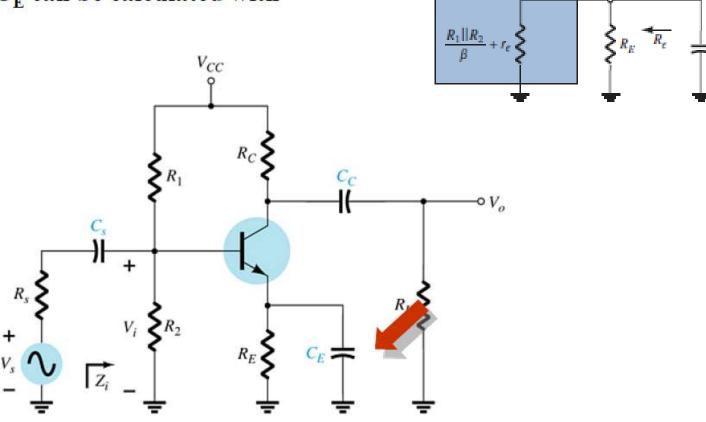

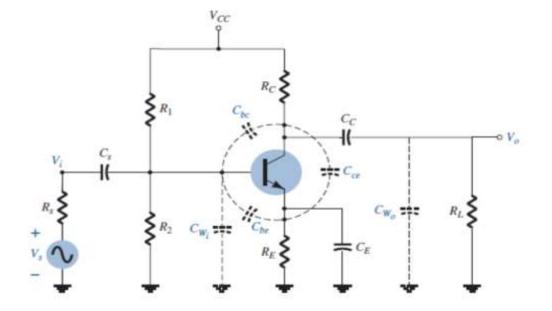

#### **RC-**Coupled BJT Amplifiers:

- One popular connection of amplifier stages is the *RC*-coupled variety shown in Fig. The name is derived from the capacitive coupling capacitor *Cc* and the fact that the load on the first stage is an *RC* combination.

- The coupling capacitor isolates the two stages from a dc viewpoint but acts as a short-circuit equivalent for the ac response. The input impedance of the second stage acts as a load on the first

R-C coupled BJT amplifiers.

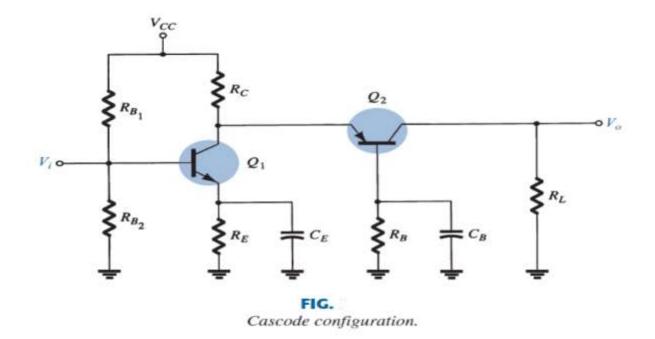

#### Cascode Connection:

- The cascode configuration has two configurations. In each case the collector of the leading transistor is connected to the emitter of the following transistor.

- The arrangements provide a relatively high-input impedance with low voltage gain for the first stage to ensure the input Miller capacitance is at a minimum, whereas the following CB stage provides an excellent high-frequency response.

# A Practical cascode Circuits:

Practical cascode circuit for Example 16.

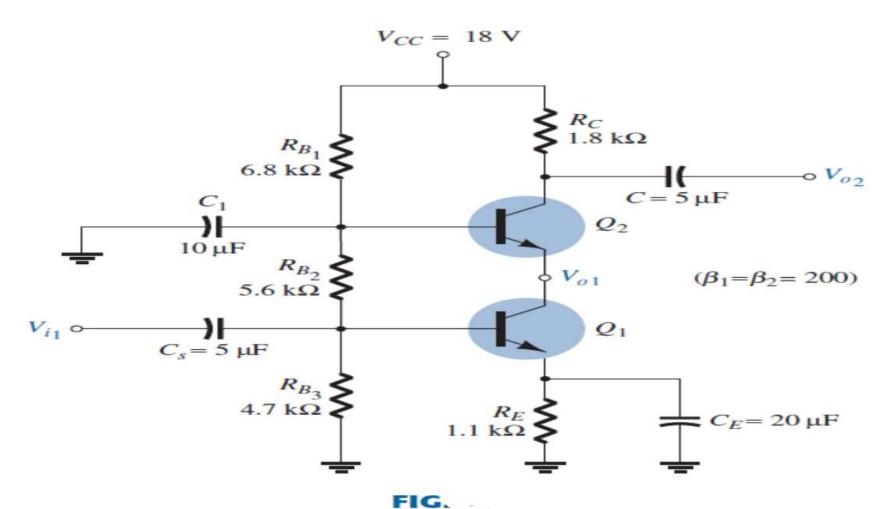

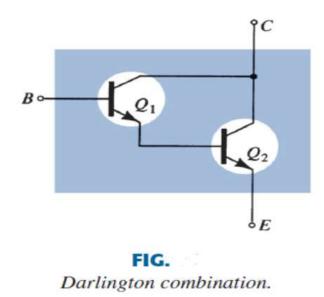

## **Darlington Connection:**

• A very popular connection of two bipolar junction transistors for operation as one "superbeta" transistor is the Darlington connection shown in Fig. The main feature of the Darlington connection is that the composite transistor acts as a single unit with a current gain that is the product of the current gains of the individual transistors. If the connection is made using two separate transistors having current gains of  $\beta_1$  and  $\beta_2$ ,

the Darlington connection provides a current gain of

$$\beta_D = \beta_1 \beta_2$$

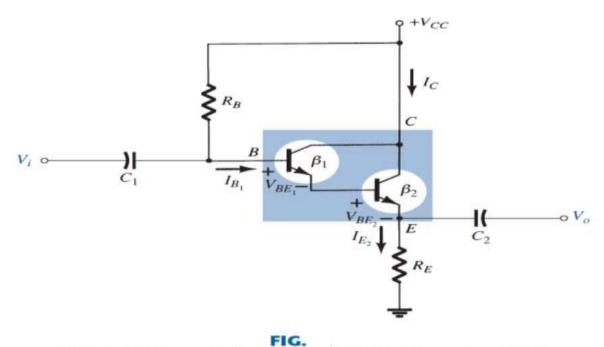

## Emitter-Follower Configuration with darlington amplifier:

• A Darlington amplifier used in an emitter-follower configuration appears in Fig. The primary impact of using the Darlington configuration is an input impedance much larger than that obtained with a single-transistor network. The current gain is also larger, but the voltage gain for a single-transistor or Darlington configuration remains slightly less than one.

Emitter-follower configuration with a Darlington amplifier.

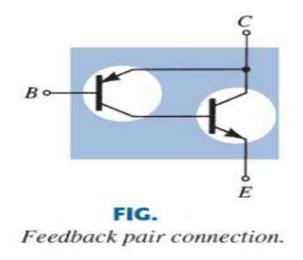

# Feedback pair:

• The feedback pair connection is a two-transistor circuit that operates like the Darlington circuit. Notice that the feedback pair uses a *pnp* transistor driving an *npn* transistor, the two devices acting effectively much like one *pnp* transistor. As with a Darlington connection, the feedback pair provides very high current gain (the product of the transistor current gains), high input impedance, low output impedance, and a voltage gain slightly less than one. Initially, it may appear that it would have a high voltage gain because the output is taken off the collector with a resistor *RC* in place. However, the *pnp-npn* combination results in terminal characteristics very similar to that of the emitter–follower configuration. A typical application uses a Darlington and a feedback-pair connection to provide complementary transistor operation.

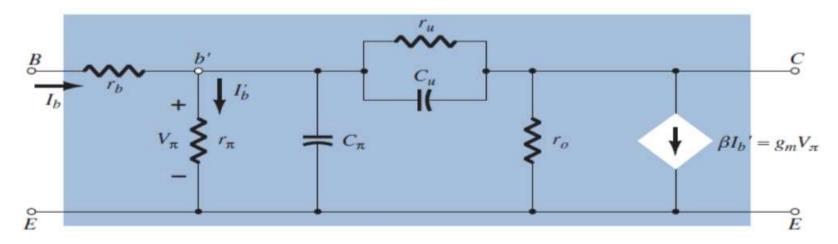

# HYBRID $\pi$ MODEL

• The last transistor model to be introduced is the hybrid pi model of Fig. which includes parameters that do not appear in the other two models primarily to provide a more accurate model for <a href="high-frequency effects">high-frequency effects</a>.

FIG.

Giacoletto (or hybrid  $\pi$ ) high-frequency transistor small-signal ac equivalent circuit.

### $r_{\pi}$ , $r_0$ , $r_b$ , and $r_u$

The resistors  $r_{\pi}$ ,  $r_{o}$ ,  $r_{b}$ , and  $r_{u}$  are the resistances between the indicated terminals of the device when the device is in the active region. The resistance  $r_{\pi}$  (using the symbol  $\pi$  to agree with the hybrid  $\pi$  terminology) is simply  $\beta r_{e}$  as introduced for the common-emitter  $r_{e}$  model. That is,

$$r_{\pi} = \beta r_e$$

The output resistance  $r_o$  is the output resistance normally appearing across an applied load. Its value, which typically lies between 5 k $\Omega$  and 40 k $\Omega$ , is determined from the hybrid parameter  $h_{oe}$ , the Early voltage, or the output characteristics.

The resistance  $r_b$  includes the base contact, base bulk, and base spreading resistance levels. The first is due to the actual connection to the base. The second includes the resistance from the external terminal to the active region of the transistor, and the last is the actual resistance within the active base region. It is typically a few ohms to tens of ohms.

The resistance  $r_u$  (the subscript u refers to the *union* it provides between collector and base terminals) is a very large resistance and provides a feedback path from output to input circuits in the equivalent model. It is typically larger than  $\beta r_o$ , which places it in the megohm range.

### $C_{\pi}$ and $C_{u}$

All the capacitors that appear in Fig. are stray parasitic capacitors between the various junctions of the device. They are all capacitive effects that really only come into play at high frequencies. For low to mid-frequencies their reactance is very large, and they can be considered open circuits. The capacitor  $C_{\pi}$  across the input terminals can range from a few pF to tens of pF. The capacitor  $C_u$  from base to collector is usually limited to a few pF but is magnified at the input and output by an effect called the Miller effect.

### $\beta I_b'$ or $g_m V_{\pi}$

It is important to note in Fig. that the controlled source can be a voltage-controlled current source (VCCS) or a current-controlled current source (CCCS), depending on the parameters employed.

$$g_m = \frac{1}{r_e}$$

$$r_o = \frac{1}{h_{oe}}$$

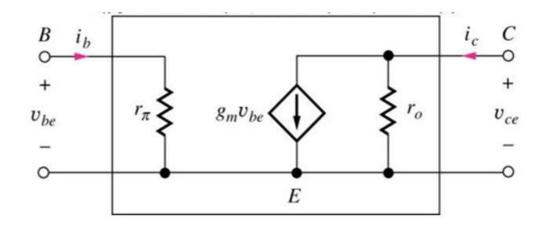

## Hybrid-Pi Model for Low frequency representation of BJT:

- The hybrid-pi small-signal model is the intrinsic low-frequency representation of the BJT.

- The small-signal parameters are control led by the Q-point and are independent of the geometry of the BJT.

Transconductance:

$$g_m = \frac{I_C}{V_T}, V_T = \frac{KT}{q}$$

Input resistance: Rin

$$r_{\pi} = \frac{\beta_o V_T}{I_C} = \frac{\beta_o}{g_m}$$

Output resistance:

$$r_o = \frac{V_A + V_{CE}}{I_C}$$

Where,  $V_A$  is Early Voltage ( $V_A$ =100V for npn)

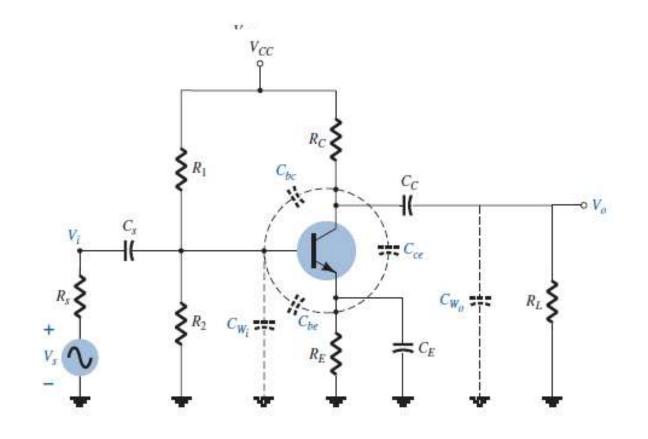

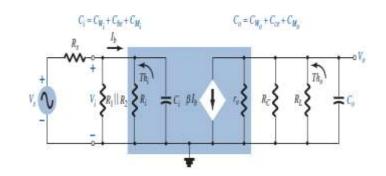

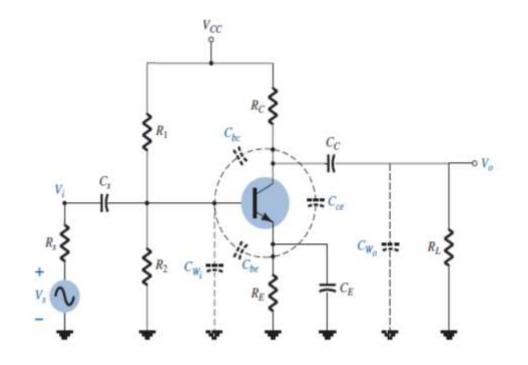

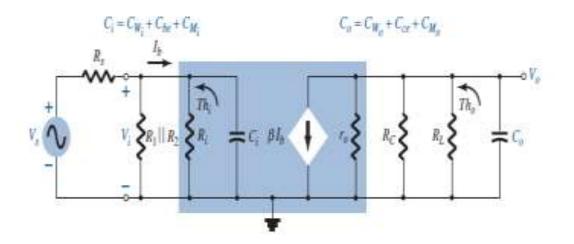

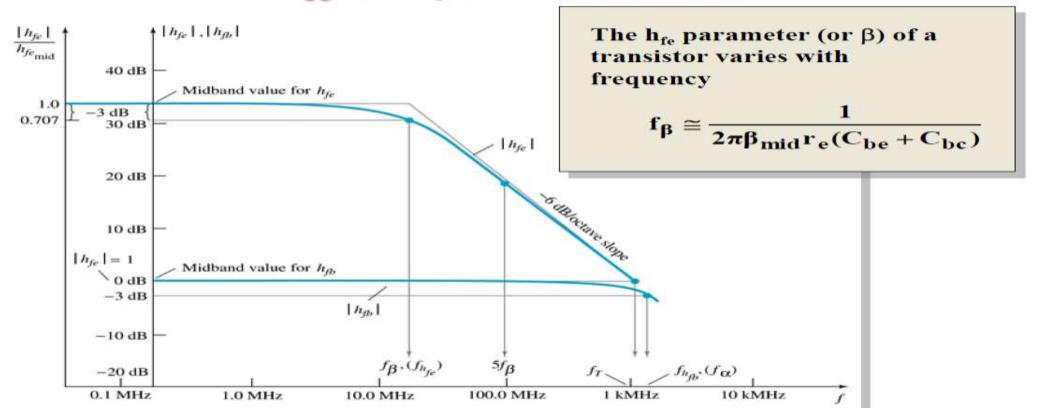

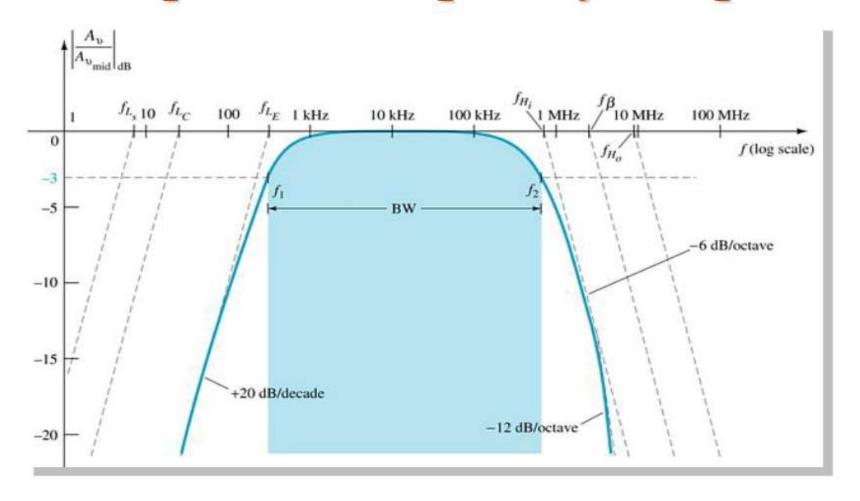

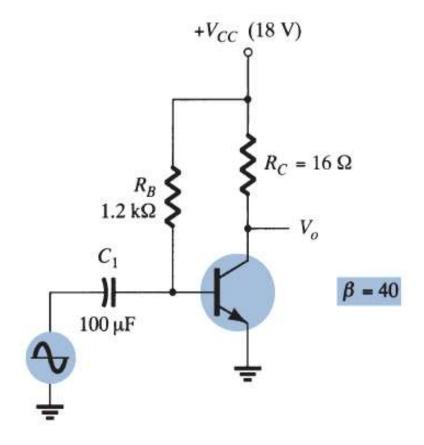

## Frequency Response of CE BJT Amplifier

$$X_C = \frac{1}{2\pi \times f \times C}$$

Assuming that the coupling and bypass capacitors are ideal shorts at the midrange signal frequency, the midrange voltage gain can be determined by

$$A_{v,mid} = \frac{(R_C \setminus \setminus R_L)}{r_e'}$$

- ➤ In the low frequency range, BJT amplifier has three high-pass RC circuits, namely input, bypass and output RC circuit, that affect its gain.

- The lower cutoff frequency of a given common emitter amplifier will be given by the highest of the individual RC circuits.

$$f_{C-low} = MAX(f_{c-input}, f_{c-output}, f_{c-bypass})$$

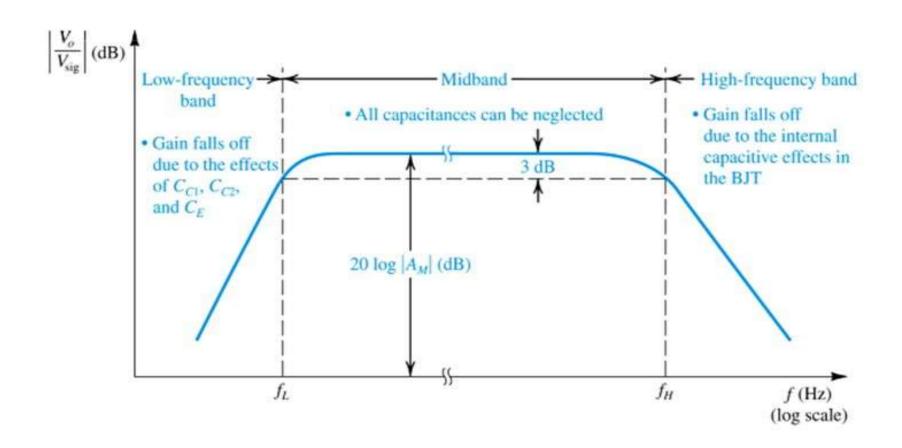

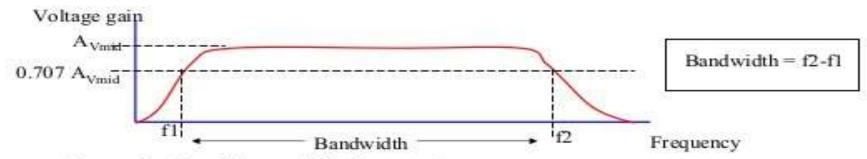

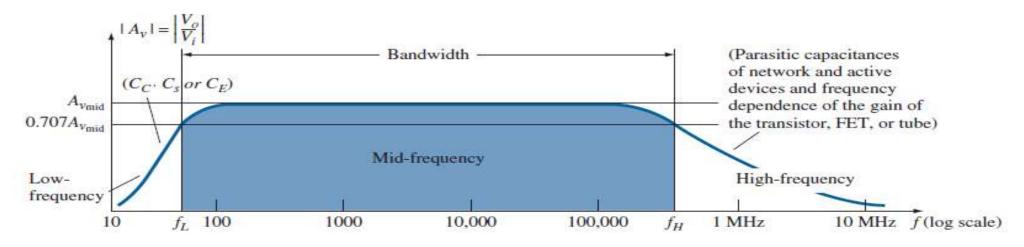

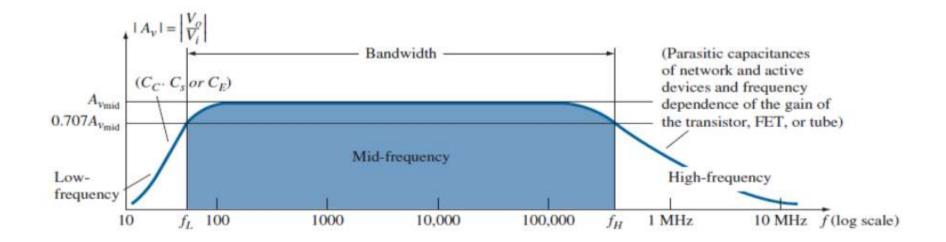

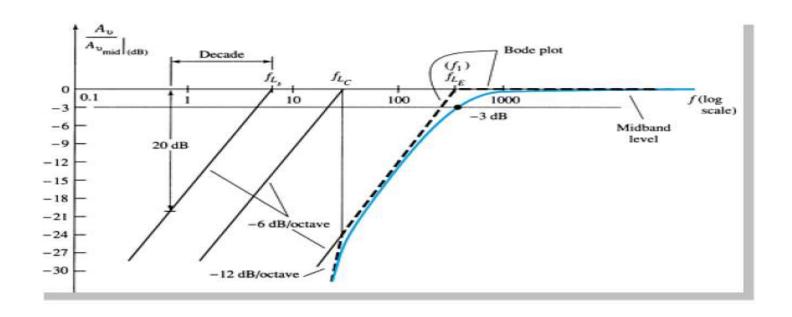

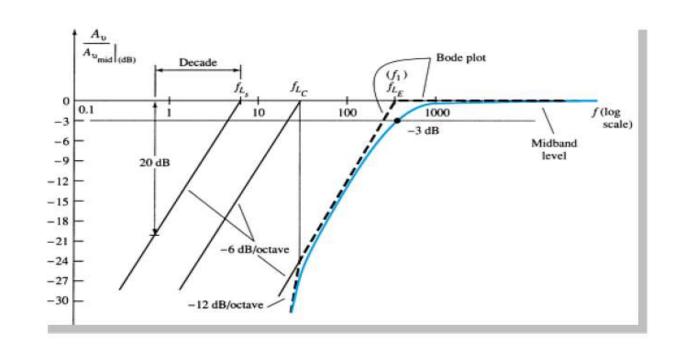

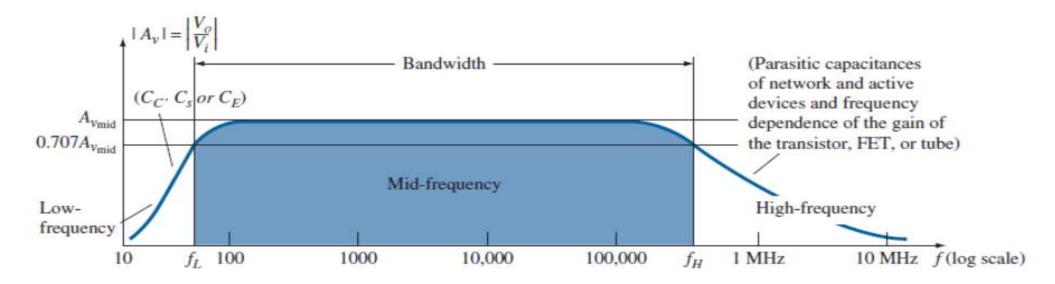

## Typical Frequency response

### Effects of Frequency on Operation of Circuits

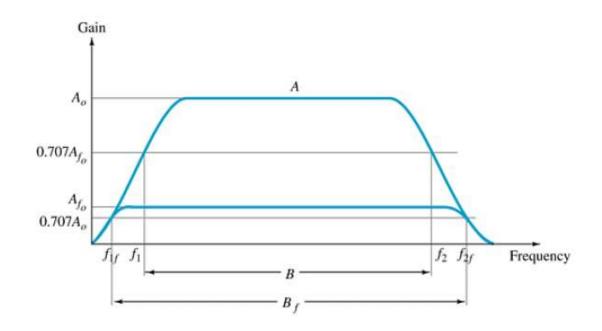

- Increase in the number of stages could also affect the frequency response of a circuit.

- In general, the gain of amplifier circuits decreases at low and high frequencies.

- The cutoff frequencies are the frequencies when the power delivered to the load of the circuit becomes half the power delivered to the load at middle frequencies.

Av<sub>mid</sub> = voltage gain of amplifier at middle frequencies

0.707 Av<sub>mid</sub> = voltage gain of amplifier at lower cutoff frequency and higher cutoff frequency (when output power is half the output power at middle frequencies)

f1 = low cutoff frequency  $P_{O(HPF)} = output power at higher cutoff frequency <math>P_{O(LPF)} = output power at lower cutoff frequency$   $P_{O(LPF)} = output power at lower cutoff frequency$

Pomid= output power at middle frequencies

$$P_{O(HPF)} = P_{O(LPF)} = \frac{(0.707 A_{vmid} \ Vi)^2}{Ro} = 0.5 \frac{(A_{vmid} \ Vi)^2}{Ro} = 0.5 \ P_{Omid}$$

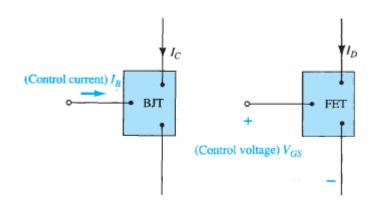

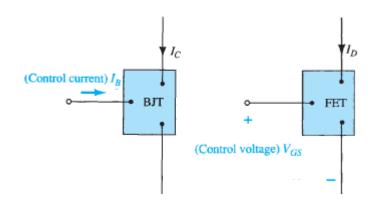

### Field Effect Transistors (FETs):

- Field effect transistors are unipolar device because current is carried by only one type of carriers (majority carriers) while BJTs were bipolar.

- FETs are voltage controlled device where output current is controlled by voltage between two terminals gate and source while BJTs were current controlled device.

FETs are characterized by very high input resistance (in mega ohm) while BJT have high gain.

FETs are less sensitive to temperature variations and are more easily integrated on ICs.

#### Types of FETs:

Junction Field Effect Transistor (JFET)

Metal Oxide semiconductor Field Effect Transistor (MOSFET)

$$I_C = \beta I_B$$

$$I_D = I_{DSS} \left( 1 - \frac{V_{GS}}{V_P} \right)^2$$

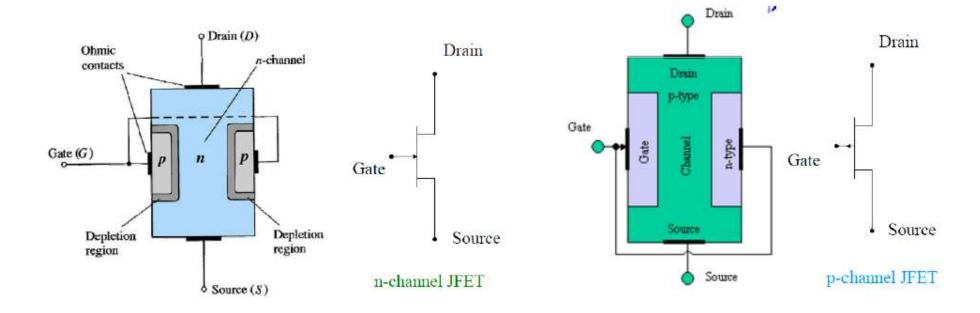

# Junction Field Effect Transistors (JFETs):

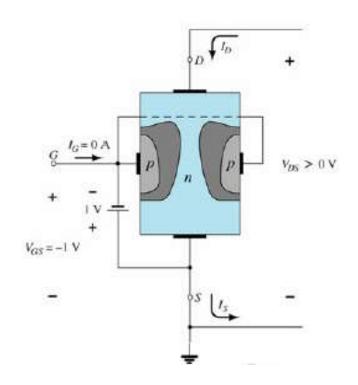

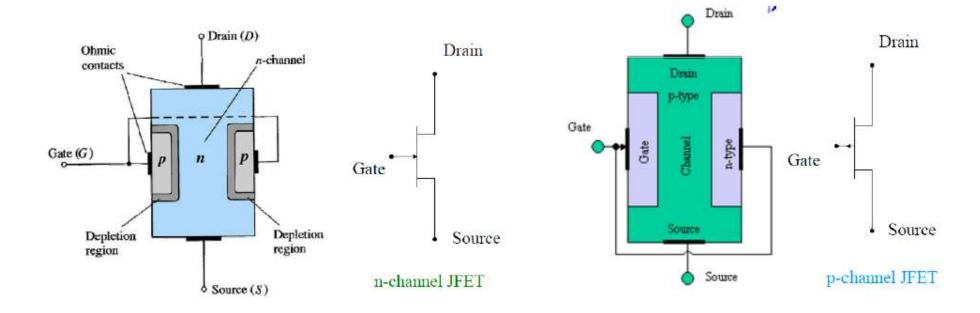

- Junction field effect transistor (JFET) is a type FET that operates with a reverse biased p-n junction to control current in a channel.

- Depending on the structure, JFET fall in two categories: n channel and p channel JFET

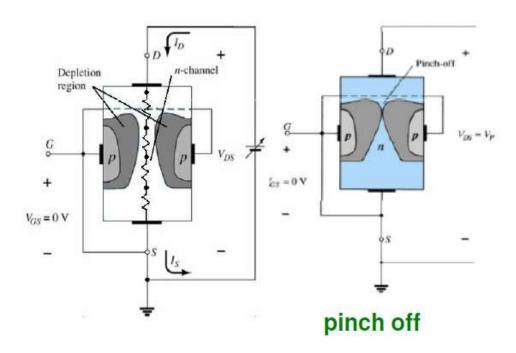

# Operation of n channel FET:

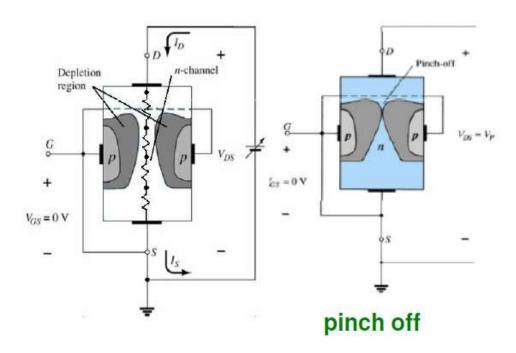

#### JFET at $V_{GS}=0$ and $V_{DS}>0$

- JFET has two p-n junction. When V<sub>GS</sub>=0, both gate and source are at same potential so depletion region in low end of each p material is similar.

- The depletion region is wider near the top of both p type material because of higher potential at upper region. (Upper end of n-channel (drain) is at V<sub>D</sub> and lower end (source) is at ground)

- The instant V<sub>DS</sub> is applied across the channel, the electrons are drawn towards the drain giving drain current.

- As the V<sub>DS</sub> is increased from 0V to a few V, the current will increase according to Ohm's law.

- As the V<sub>DS</sub> approaches to Vp, the depletion width increases causing a reduction in channel width.

- The value of  $V_{DS}$  (at  $V_{GS}$ =0) for which two depletion region touches is called pinch off voltage and denoted by  $V_P$ .

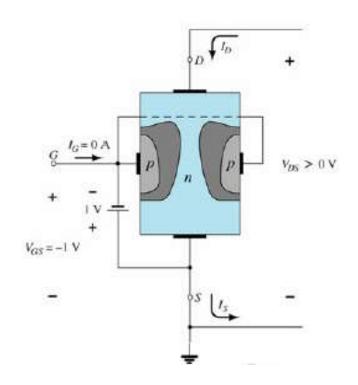

#### JFET at V<sub>GS</sub> < 0 and V<sub>DS</sub> > 0

The level of V<sub>GS</sub> that results in I<sub>D</sub> = 0 mA is V<sub>GS</sub> = V<sub>P</sub> Vp is a negative voltage for n-channel and positive for p-channel JFETs.

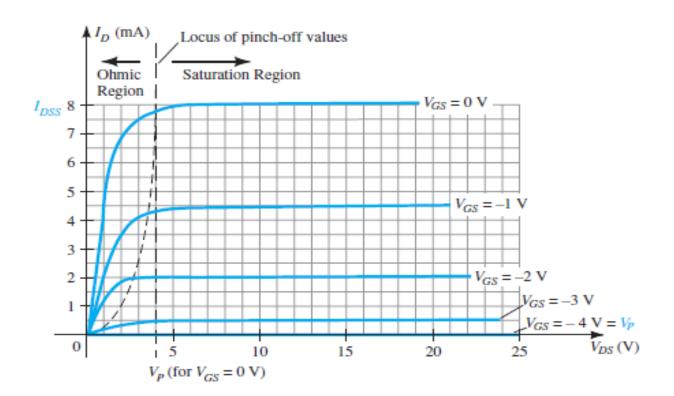

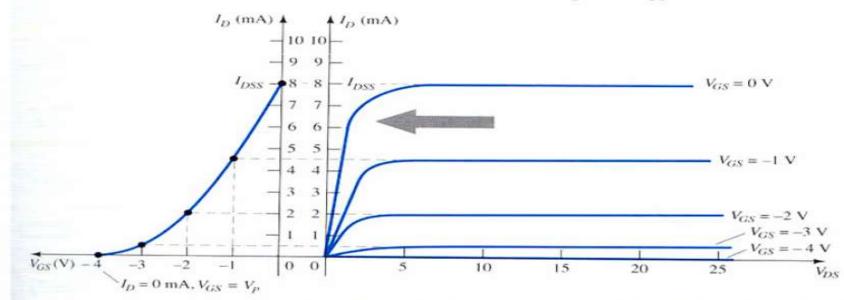

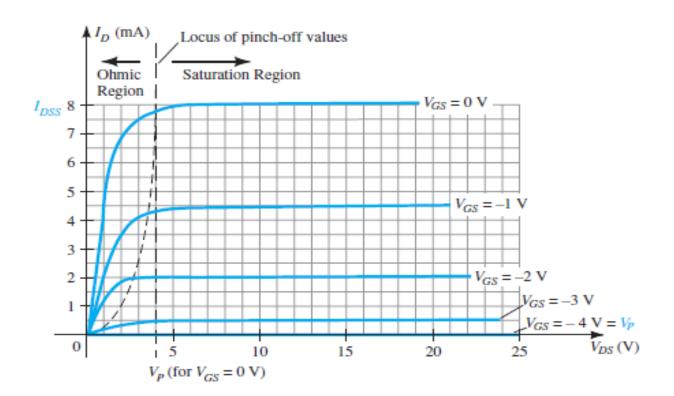

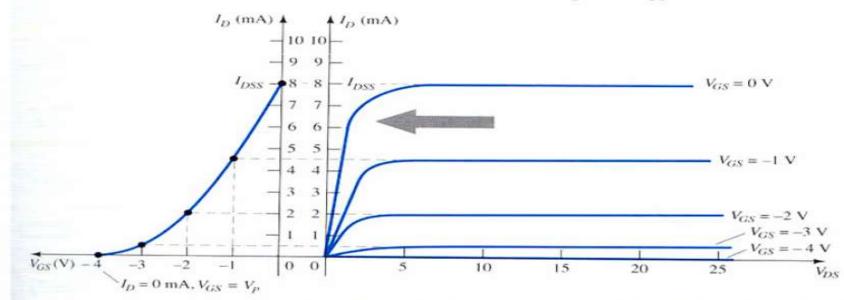

#### **Transfer Characteristics**

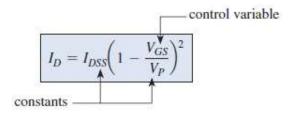

The relationship between  $I_D$  and  $V_{GS}$  is defined by Shockley's equation:

$$oldsymbol{I}_D = oldsymbol{I}_{DSS} iggl( 1 - rac{oldsymbol{V}_{GS}}{oldsymbol{V}_P} iggr)^2$$

Where  $\emph{I}_{DSS}$  and  $\emph{V}_{P}$  are constants and  $\emph{V}_{GS}$  is variable and controllable

The transfer function curve may be plotted from the characteristic curve, as shown. Notice the parabolic shape due to the square term relationship between  $I_D$  and  $V_{GS}$

Remember that, when  $V_{GS} = 0$ ,  $I_D = I_{DSS}$  and when  $V_{GS} = V_P$ ,  $I_D = 0$  mA

## Contents of the Class:

- Biasing of the JFET

- 1)FET in fixed bias

- 2)Self-bias

- 3) Voltage Divider Biasing

• From book- R. L. Boylestad

## Basic of Field Effect Transistors (FETs):

- Field effect transistors are unipolar device because current is carried by only one type of carriers (majority carriers) while BJTs were bipolar.

- FETs are voltage controlled device where output current is controlled by voltage between two terminals gate and source while BJTs were current controlled device.

FETs are characterized by very high input resistance (in mega ohm) while BJT have high gain.

FETs are less sensitive to temperature variations and are more easily integrated on ICs.

### **Types of FETs:**

Junction Field Effect Transistor (JFET)

Metal Oxide semiconductor Field Effect Transistor (MOSFET)

$$I_C = \beta I_B$$

$$I_D = I_{DSS} \left( 1 - \frac{V_{GS}}{V_P} \right)^2$$

# Junction Field Effect Transistors (JFETs):

- Junction field effect transistor (JFET) is a type FET that operates with a reverse biased p-n junction to control current in a channel.

- Depending on the structure, JFET fall in two categories: n channel and p channel JFET

# Operation of n channel FET:

#### JFET at $V_{GS}=0$ and $V_{DS}>0$

- JFET has two p-n junction. When V<sub>GS</sub>=0, both gate and source are at same potential so depletion region in low end of each p material is similar.

- The depletion region is wider near the top of both p type material because of higher potential at upper region. (Upper end of n-channel (drain) is at V<sub>D</sub> and lower end (source) is at ground)

- The instant V<sub>DS</sub> is applied across the channel, the electrons are drawn towards the drain giving drain current.

- As the V<sub>DS</sub> is increased from 0V to a few V, the current will increase according to Ohm's law.

- As the V<sub>DS</sub> approaches to Vp, the depletion width increases causing a reduction in channel width.

- The value of  $V_{DS}$  (at  $V_{GS}$ =0) for which two depletion region touches is called pinch off voltage and denoted by  $V_P$ .

#### JFET at V<sub>GS</sub> < 0 and V<sub>DS</sub> > 0

The level of V<sub>GS</sub> that results in I<sub>D</sub> = 0 mA is V<sub>GS</sub> = V<sub>P</sub> Vp is a negative voltage for n-channel and positive for p-channel JFETs.

#### **Transfer Characteristics**

The relationship between  $I_D$  and  $V_{GS}$  is defined by Shockley's equation:

$$oldsymbol{I}_D = oldsymbol{I}_{DSS} iggl( 1 - rac{oldsymbol{V}_{GS}}{oldsymbol{V}_P} iggr)^2$$

Where  $\emph{I}_{DSS}$  and  $\emph{V}_{P}$  are constants and  $\emph{V}_{GS}$  is variable and controllable

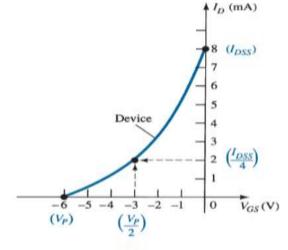

The transfer function curve may be plotted from the characteristic curve, as shown. Notice the parabolic shape due to the square term relationship between  $I_D$  and  $V_{GS}$

Remember that, when  $V_{GS} = 0$ ,  $I_D = I_{DSS}$  and when  $V_{GS} = V_P$ ,  $I_D = 0$  mA

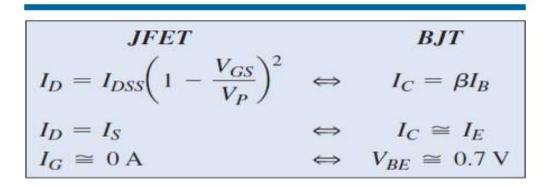

## Important Relationship:

A number of important equations and operating characteristics for the JFET have been introduced that are of particular importance for the analysis of dc and ac configurations that will follow.

Recall that VBE = 0.7 V was

often the key to initiating an analysis of a BJT configuration. Similarly, the condition  $I_G = 0$  A is often the starting point for the analysis of a JFET configuration. For the BJT configuration,  $I_B$  is normally the first parameter to be determined. For the JFET, it is normally  $V_{GS}$ .

# FIG. (a) JFET versus (b) BJT.

## FET Biasing:

- For the field-effect transistor, the relationship between input and output quantities is *nonlinear* due to the squared term in Shockley's equation. Linear relationships result in straight lines when plotted on a graph of one variable versus the other, whereas nonlinear functions result in curves as obtained for the transfer characteristics of a JFET. The nonlinear relationship between ID and VGS can complicate the mathematical approach to the dc analysis of FET configurations.

- A graphical approach may limit solutions to tenths-place accuracy, but it is a quicker method for most FET amplifiers.

The general relationships that can be applied to the dc analysis of all FET amplifiers are

$$I_G \cong 0 A$$

and

$$I_D = I_S$$

For JFETs and depletion-type MOSFETs and MESFETs, Shockley's equation is applied to relate the input and output quantities:

$$I_D = I_{DSS} \left( 1 - \frac{V_{GS}}{V_P} \right)^2$$

For enhancement-type MOSFETs and MESFETs, the following equation is applicable:

$$I_D = k(V_{GS} - V_T)^2$$

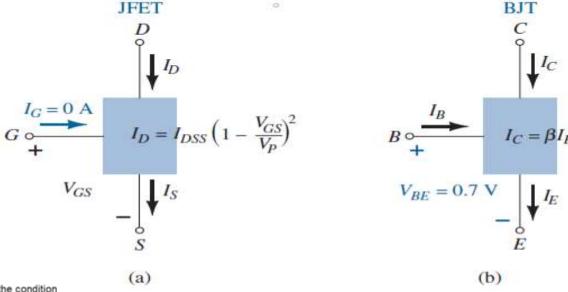

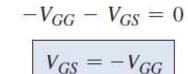

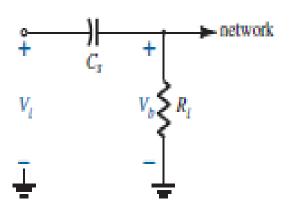

## Fixed-Bias Configuration:

The simplest of biasing arrangements for the n-channel JFET appears FET configurations that can be solved just as directly using either a **mathematical or a graphical approach**. The coupling capacitors are "open circuits" for the dc analysis and low impedances (essentially short circuits) for the ac analysis. The resistor  $R_G$  is present to ensure that  $V_i$  appears at the input to the FET amplifier for the ac analysis. For the dc analysis.

#### **Fixed-Bias Configuration:**

• The zero-volt drop across  $R_G$  permits replacing  $R_G$  by a short-circuit equivalent, as appearing in the network of specifically redrawn for the dc analysis.

Applying Kirchhoff's voltage law in the clockwise direction of the indicated loop

Since  $V_{GG}$  is a fixed dc supply, the voltage  $V_{GS}$  is fixed in magnitude, resulting in the designation "fixed-bias configuration."

Network for dc analysis.

The resulting level of drain current  $I_D$  is now controlled by Shockley's equation:

$$I_D = I_{DSS} \left( 1 - \frac{V_{GS}}{V_P} \right)^2$$

Since *VGS* is a fixed quantity for this configuration, its magnitude and sign can simply be substituted into Shockley's equation and the resulting level of *ID* calculated.

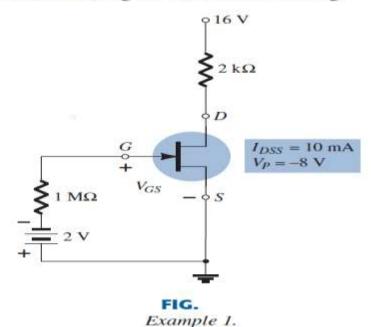

### A graphical analysis

A graphical analysis would require a plot of Shockley's equation as shown in Fig.

Recall that choosing  $V_{GS} = V_P/2$  will result in a drain current of  $I_{DSS}/4$  when plotting the equation. For the analysis of this chapter, the three points defined by  $I_{DSS}$ ,  $V_P$ , and the intersection just described will be sufficient for plotting the curve.

In Fig. the fixed level of  $V_{GS}$  has been superimposed as a vertical line at  $V_{GS} = -V_{GG}$ . At any point on the vertical line, the level of  $V_{GS}$  is  $-V_{GG}$ —the level of  $I_D$  must simply be determined on this vertical line. The point where the two curves intersect is the common solution to the configuration—commonly referred to as the *quiescent* or *operating point*. The subscript Q will be applied to the drain current and gate-to-source voltage to identify their levels at the Q-point. Note in Fig. that the quiescent level of  $I_D$  is determined by drawing a horizontal line from the Q-point to the vertical  $I_D$  axis.

FIG.

Finding the solution for the fixed-bias configuration.

The drain-to-source voltage of the output section can be determined by applying Kirchhoff's voltage law as follows:

$$+V_{DS}+I_DR_D-V_{DD}=0$$

and

$$V_{DS} = V_{DD} - I_D R_D$$

Recall that single-subscript voltages refer to the voltage at a point with respect to ground.

$$V_S = 0 \text{ V}$$

Using double-subscript notation, we have

or

$$V_{DS} = V_D - V_S$$

$$V_D = V_{DS} + V_S = V_{DS} + 0 \text{ V}$$

and

$$V_D = V_{DS}$$

In addition,

$$V_{GS} = V_G - V_S$$

$$V_G = V_{GS} + V_S = V_{GS} + 0 \text{ V}$$

and

or

$$V_G = V_{GS}$$

The fact that  $V_D = V_{DS}$  and  $V_G = V_{GS}$  is fairly obvious from the fact that  $V_S = 0 \text{ V}$ , but the derivations above were included to emphasize the relationship that exists between double-subscript and single-subscript notation. Since the configuration requires two dc supplies, its use is limited and will not be included in the forthcoming list of the most common FET configurations.

Network for dc analysis.

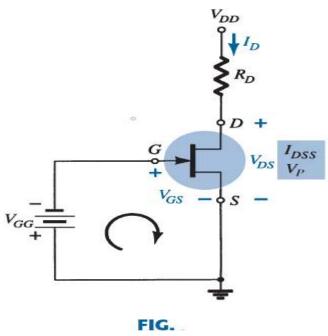

#### **EXAMPLE 1** Determine the following for the network of Fig.

- a.  $V_{GS_O}$ .

- b.  $I_{D_Q}$ .

- c. VDS.

- d.  $V_D$ .

- e.  $V_G$ .

- f.  $V_S$ .

#### Solution:

### **Mathematical Approach**

a.

$$V_{GS_Q} = -V_{GG} = -2 \text{ V}$$

b.

$$I_{D_Q} = I_{DSS} \left( 1 - \frac{V_{GS}}{V_P} \right)^2 = 10 \text{ mA} \left( 1 - \frac{-2 \text{ V}}{-8 \text{ V}} \right)^2$$

=  $10 \text{ mA} (1 - 0.25)^2 = 10 \text{ mA} (0.75)^2 = 10 \text{ mA} (0.5625)$

=  $5.625 \text{ mA}$

c.

$$V_{DS} = V_{DD} - I_D R_D = 16 \text{ V} - (5.625 \text{ mA})(2 \text{ k}\Omega)$$

= 16 V - 11.25 V = **4.75 V**

d.

$$V_D = V_{DS} = 4.75 \text{ V}$$

e.

$$V_G = V_{GS} = -2 \text{ V}$$

f.

$$V_S = 0 \text{ V}$$

## **Graphical Approach** are provided in Fig.

The resulting Shockley curve and the vertical line at  $V_{GS} = -2 \text{ V}$ It is certainly difficult to read beyond the second place without

Graphical solution for the network

$$V_{GS_O} = -V_{GG} = -2 \text{ V}$$

b.

$$I_{D_0} = 5.6 \text{ mA}$$

c.

$$V_{DS} = V_{DD} - I_D R_D = 16 \text{ V} - (5.6 \text{ mA})(2 \text{ k}\Omega)$$

=  $16 \text{ V} - 11.2 \text{ V} = 4.8 \text{ V}$

d.

$$V_D = V_{DS} = 4.8 \text{ V}$$

e.

$$V_G = V_{GS} = -2 \text{ V}$$

f.

$$V_S = \mathbf{0} \mathbf{V}$$

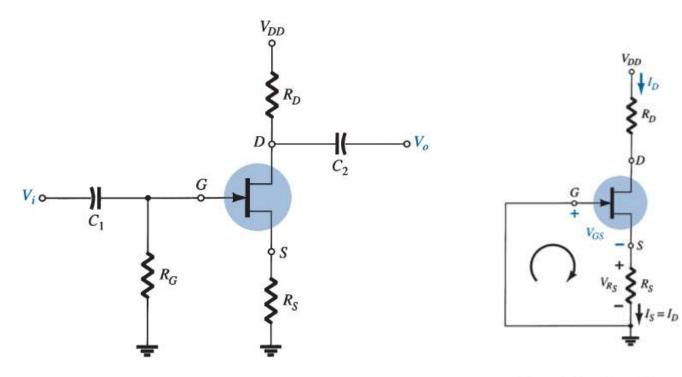

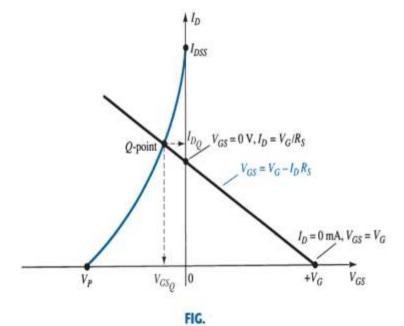

### **Self-Bias Configuration:**

The self-bias configuration eliminates the need for two dc supplies. The controlling gateto-source voltage is now determined by the voltage across a resistor *Rs* introduced in the source leg of the configuration as shown in Fig.

JFET self-bias configuration.

DC analysis of the self-bias configuration.

For the dc analysis, the capacitors can again be replaced by "open circuits" and the resistor  $R_G$  replaced by a short-circuit equivalent since  $I_G = 0$  A.

The current through  $R_S$  is the source current  $I_S$ , but  $I_S = I_D$  and

$$V_{R_S} = I_D R_S$$

For the indicated closed loop of Fig. 9, we find that

$$-V_{GS}-V_{R_S}=0$$

and

$$V_{GS} = -V_{R_S}$$

or

$$V_{GS} = -I_D R_S$$

Note in this case that *VGS* is a function of the output current *ID* and not fixed in magnitude as occurred for the fixed-bias configuration.

Drain Current (ID) can be calculated from Shockley equation using mathematical or a graphical Approach.

DC analysis of the self-bias configuration.

A mathematical solution could be obtained simply by substituting Eq.

$$V_{GS} = -I_D R_S$$

in Shockley equation.

$$I_D = I_{DSS} \left( 1 - \frac{V_{GS}}{V_P} \right)^2$$

$$= I_{DSS} \left( 1 - \frac{-I_D R_S}{V_P} \right)^2$$

$$I_D = I_{DSS} \left( 1 + \frac{I_D R_S}{V_P} \right)^2$$

or

By performing the squaring process indicated and rearranging terms, we obtain an equation of the following form:

$$I_D^2 + K_1 I_D + K_2 = 0$$

The quadratic equation can then be solved for the appropriate solution for  $I_D$ .

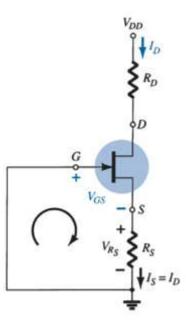

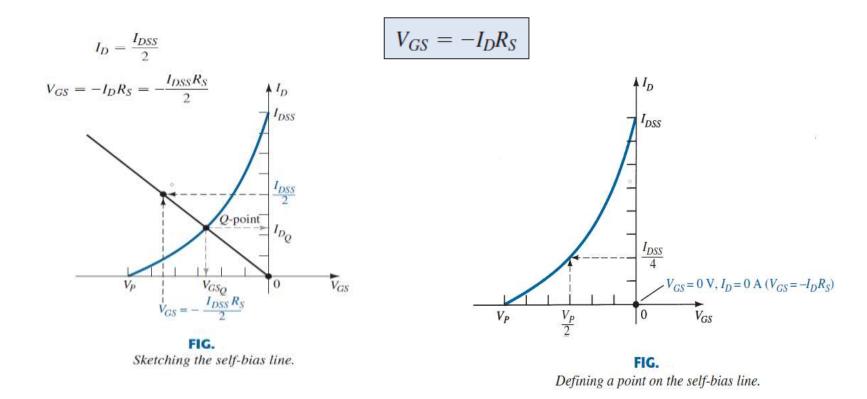

## The graphical approach:

The graphical approach requires that we first establish the device transfer characteristics as shown in Fig.

The quiescent values of *I*<sub>D</sub> and *V*<sub>GS</sub> can then be determined and used to find the other quantities of interest.

The level of  $V_{DS}$  can be determined by applying Kirchhoff's voltage law to the output circuit, with the result that

$$V_{R_S} + V_{DS} + V_{R_D} - V_{DD} = 0$$

$$V_{DS} = V_{DD} - V_{R_S} - V_{R_D} = V_{DD} - I_S R_S - I_D R_D$$

and

$$I_D = I_S$$

$$V_{DS} = V_{DD} - I_D(R_S + R_D)$$

$$V_S = I_D R_S$$

$$V_G = 0 \text{ V}$$

$$V_D = V_{DS} + V_S = V_{DD} - V_{R_D}$$

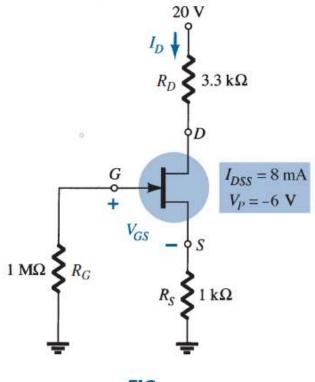

#### **EXAMPLE 2** Determine the following for the network of Fig.

- a.  $V_{GS_Q}$ . b.  $I_{D_Q}$ . c.  $V_{DS}$ . d.  $V_S$ . e.  $V_G$ . f.  $V_D$ .

FIG. Example 2.

### Solution:

a. The gate-to-source voltage is determined by

$$V_{GS} = -I_D R_S$$

Choosing  $I_D = 4 \text{ mA}$ , we obtain

$$V_{GS} = -(4 \text{ mA})(1 \text{ k}\Omega) = -4 \text{ V}$$

$V_{GS_Q} = -2.6 \text{ V}$  $I_{D_0} = 2.6 \, \text{mA}$

By using Graphical Method

If we happen to choose  $I_D = 8 \text{ mA}$ , the resulting value of  $V_{GS}$  would be -8 V,

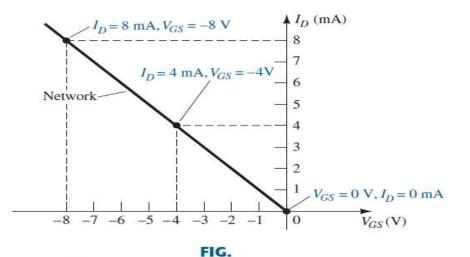

Sketching the self-bias line for the network

FIG. Sketching the device characteristics for the JFET

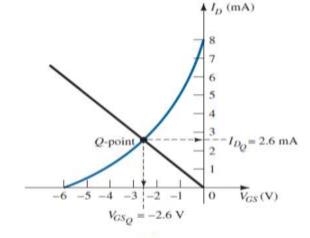

FIG. Determining the Q-point for the network of

From the graphs  $I_{D_Q} = 2.6 \,\mathrm{mA}$   $V_{GS_Q} = -2.6 \,\mathrm{V}$

$$V_{DS} = V_{DD} - I_D(R_S + R_D)$$

$= 20 \text{ V} - (2.6 \text{ mA})(1 \text{ k}\Omega + 3.3 \text{ k}\Omega)$

$= 20 \text{ V} - 11.18 \text{ V}$

$= 8.82 \text{ V}$

$V_S = I_D R_S$

$= (2.6 \text{ mA})(1 \text{ k}\Omega)$

$= 2.6 \text{ V}$

$V_G = 0 \text{ V}$

$V_D = V_{DS} + V_S = 8.82 \text{ V} + 2.6 \text{ V} = 11.42 \text{ V}$

$V_D = V_{DD} - I_D R_D = 20 \text{ V} - (2.6 \text{ mA})(3.3 \text{ k}\Omega) = 11.42 \text{ V}$

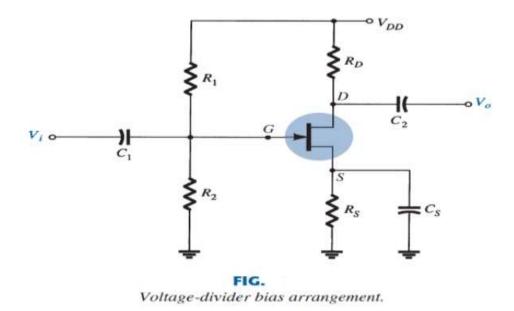

# Voltage-Divider Biasing:

$V_{DD}$   $R_1$   $R_1$   $R_2$   $R_3$   $R_4$   $R_5$   $R_6$   $R_7$   $R_8$   $R_8$   $R_8$   $R_8$   $R_8$   $R_8$   $R_9$   $R_9$  R

The voltage  $V_G$ , equal to the voltage across  $R_2$ , can be found using the voltage-divider rule.

$$V_G = \frac{R_2 V_{DD}}{R_1 + R_2}$$

### Applying Kirchhoff's voltage law in the clockwise direction to the indicated loop

and

$$V_G - V_{GS} - V_{R_S} = 0$$

$$V_{GS} = V_G - V_{R_S}$$

Substituting  $V_{R_S} = I_S R_S = I_D R_S$ , we have

$$V_{GS} = V_G - I_D R_S$$

#### For one point ID=0mA

$$V_{GS} = V_G - I_D R_S$$

=  $V_G - (0 \text{ mA}) R_S$

$$V_{GS} = V_G|_{I_D = 0 \text{ mA}}$$

Sketching the network equation for the voltage-divider configuration.

For the other point, let us now employ the fact that at any point on the vertical axis  $V_{GS} = 0 \text{ V}$  and solve for the resulting value of  $I_D$ :

$$V_{GS} = V_G - I_D R_S$$

$$0 V = V_G - I_D R_S$$

and

$$I_D = \frac{V_G}{R_S} \bigg|_{V_{GS} = 0 \text{ V}}$$

# Increasing values of $R_S$ result in lower quiescent values of $I_D$ and declining values of $V_{GS}$ .

Once the quiescent values of  $I_{Do}$  and  $V_{GS_O}$  are determined, the remaining network analysis can be performed in the usual manner. That is,

$$V_{DS} = V_{DD} - I_D(R_D + R_S)$$

$$V_D = V_{DD} - I_D R_D$$

$$V_S = I_D R_S$$

$$V_S = I_D R_S$$

$$I_{R_1} = I_{R_2} = \frac{V_{DD}}{R_1 + R_2}$$

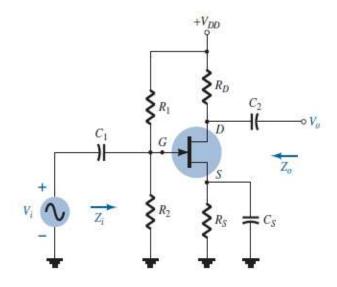

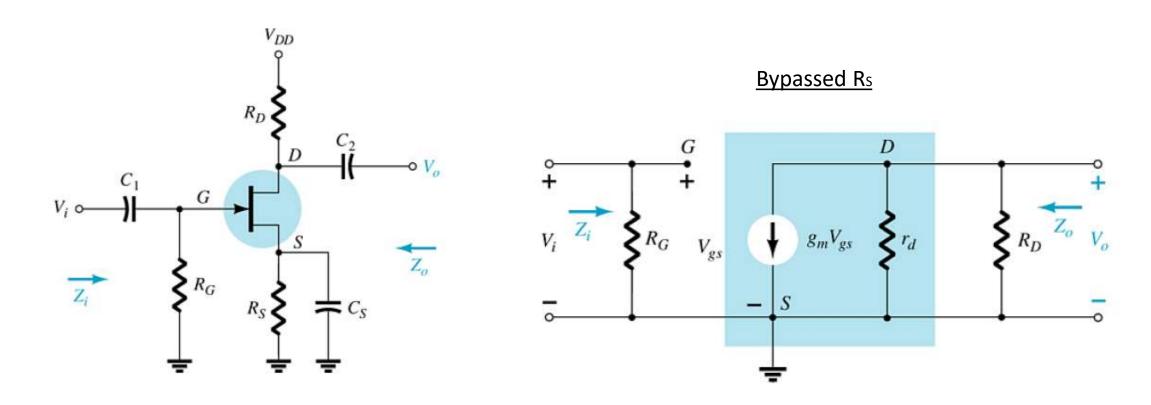

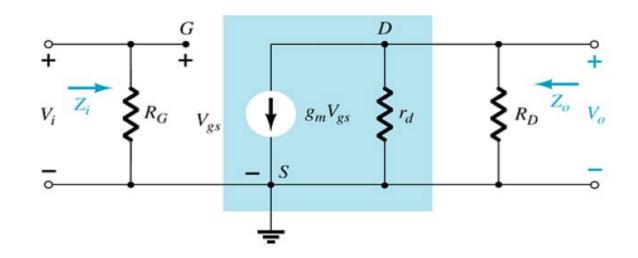

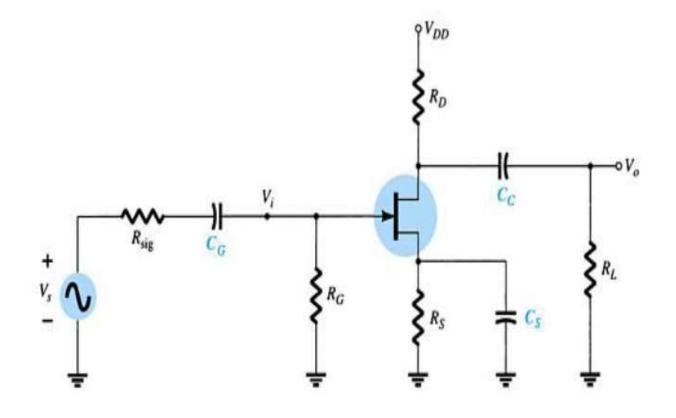

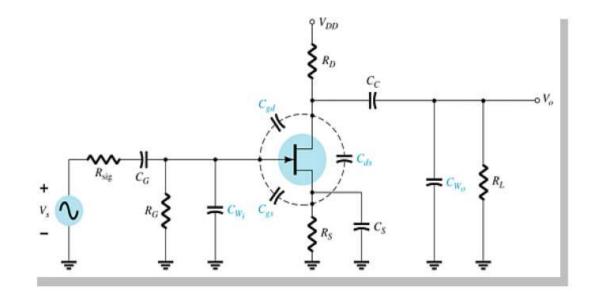

# Contents of the Class:

- FET small signal modelling

- -Fixed bias

- -Voltage divider bias

Book-R L Boylestad

# JFET small-signal Model:

- Field-effect transistor amplifiers provide an excellent voltage gain with the added feature of a high input impedance.

- The FET can be used as a linear amplifier or as a digital device in logic circuits.

- FET devices are also widely used in high-frequency applications and in buffering (interfacing) applications.

- Whereas the voltage gain of an FET amplifier is generally less than that obtained using a BJT amplifier, the FET amplifier provides a much higher input impedance than that of a BJT configuration.

# JFET small-signal Model:

- The ac analysis of a JFET configuration requires that a small-signal ac model for the JFET be developed.

- The gate-to-source voltage controls the drain-to-source (channel) current of a JFET.

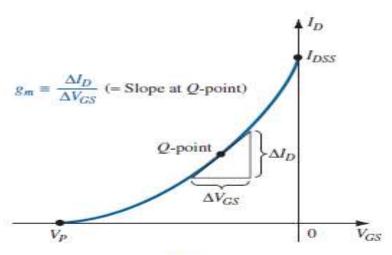

#### **Transcoductance**(g<sub>m</sub>)

• The *change* in drain current that will result from a *change* in gate-to-source voltage can be determined using the transconductance factor  $g_m$  in the following manner:

$$\Delta I_D = g_m \, \Delta V_{GS}$$

$$g_m = \frac{\Delta I_D}{\Delta V_{GS}}$$

#### Mathematical definition of $g_m$

If we therefore take the derivative of  $I_D$  with respect to  $V_{GS}$  (differential calculus) using Shockley's equation, we can derive an equation for  $g_m$  as follows:

$$\begin{split} g_{m} &= \frac{dI_{D}}{dV_{GS}} \Big|_{Q\text{-pt.}} = \frac{d}{dV_{GS}} \Big[ I_{DSS} \Big( 1 - \frac{V_{GS}}{V_{P}} \Big)^{2} \Big] \\ &= I_{DSS} \frac{d}{dV_{GS}} \Big( 1 - \frac{V_{GS}}{V_{P}} \Big)^{2} = 2I_{DSS} \Big[ 1 - \frac{V_{GS}}{V_{P}} \Big] \frac{d}{dV_{GS}} \Big( 1 - \frac{V_{GS}}{V_{P}} \Big) \\ &= 2I_{DSS} \Big[ 1 - \frac{V_{GS}}{V_{P}} \Big] \Big[ \frac{d}{dV_{GS}} (1) - \frac{1}{V_{P}} \frac{dV_{GS}}{dV_{GS}} \Big] = 2I_{DSS} \Big[ 1 - \frac{V_{GS}}{V_{P}} \Big] \Big[ 0 - \frac{1}{V_{P}} \Big] \end{split}$$

and

$$g_m = \frac{2I_{DSS}}{|V_P|} \left[ 1 - \frac{V_{GS}}{V_P} \right]$$

$$g_m = m = \frac{\Delta y}{\Delta x} = \frac{\Delta I_D}{\Delta V_{GS}}$$

FIG.

Definition of g<sub>m</sub> using transfer characteristic.

• Plugging in VGS = 0 V into the below Eq. results in the following equation for the maximum value of *gm* for a JFET in which IDSS and VP have been specified:

$$g_m = \frac{2I_{DSS}}{|V_P|} \left[ 1 - \frac{V_{GS}}{V_P} \right]$$

$$g_m = \frac{2I_{DSS}}{|V_P|} \left[ 1 - \frac{0}{V_P} \right]$$

$$g_{m0} = \frac{2I_{DSS}}{|V_P|}$$

$$g_m = g_{m0} \left[ 1 - \frac{V_{GS}}{V_P} \right]$$

# **Input impedance Zi of JFET:**

The input impedance of all commercially available JFETs is sufficiently large.

$$Z_i(JFET) = \infty \Omega$$

For a JFET a practical value of  $10^9~\Omega$  (1000 M $\Omega$ ) is typical, whereas a value of  $10^{12}~\Omega$  to  $10^{15}~\Omega$  is typical for MOSFETs and MESFETs.

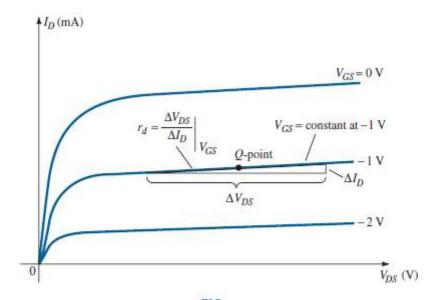

### Output impedance Zo Of JFET:

$$Z_o(\text{JFET}) = r_d = \frac{1}{g_{os}} = \frac{1}{y_{os}}$$

$$r_d = \frac{\Delta V_{DS}}{\Delta I_D}\bigg|_{V_{GS} = \text{constant}}$$

The parameter  $y_{0s}$  is a component of an *admittance equivalent circuit*, with the subscript *o* signifying an *o*utput network parameter and *s* the terminal (*s*ource) to which it is attached in the model.

**FIG.**Definition of r<sub>d</sub> using JFET drain characteristics.

The output impedance is defined on the characteristics of Fig. as the slope of the horizontal characteristic curve at the point of operation. The more horizontal the curve, the greater is the output impedance.

$$r_d = \frac{\Delta V_{DS}}{\Delta I_D}\bigg|_{V_{GS} = \text{constant}}$$

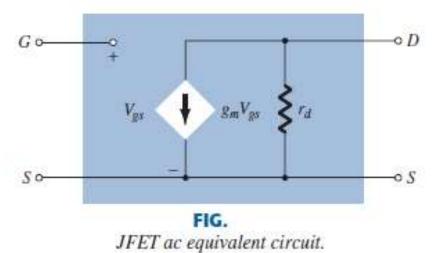

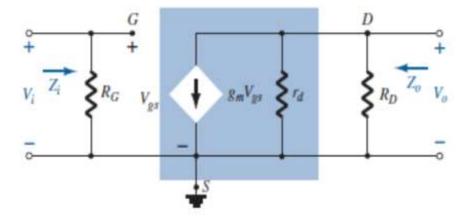

# JFET AC Equivalent Circuit:

$$g_m = \frac{2I_{DSS}}{|V_P|} \left[ 1 - \frac{V_{GS}}{V_P} \right]$$

$$Z_o$$

(JFET) =  $r_d = \frac{1}{g_{os}} = \frac{1}{y_{os}}$

$$r_d = \left. \frac{\Delta V_{DS}}{\Delta I_D} \right|_{V_{GS} = {

m constant}}$$

The equivalent circuit is simply a current source whose magnitude is controlled by the signal  $V_{gs}$  and parameter  $g_m$ —clearly a voltage-controlled current source parallel with output impedance  $r_d$ .

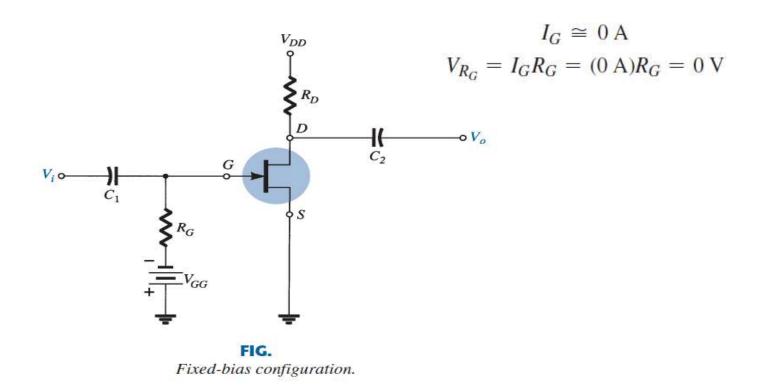

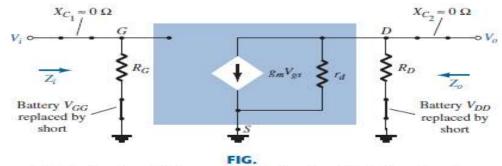

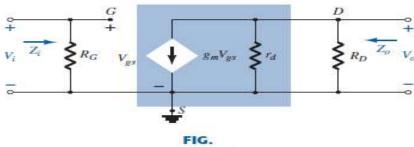

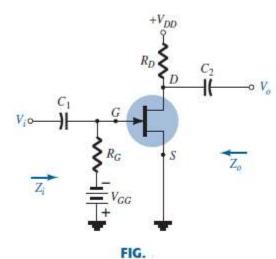

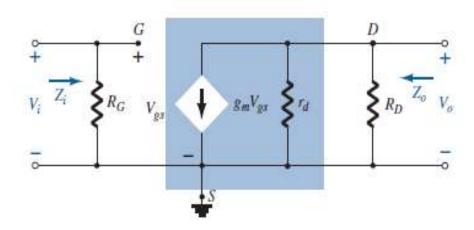

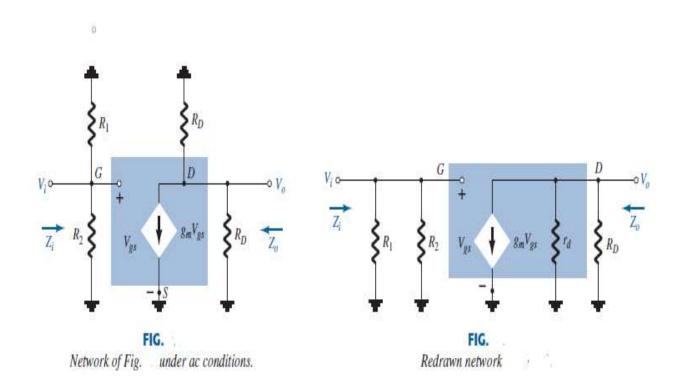

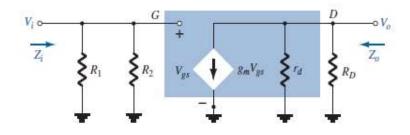

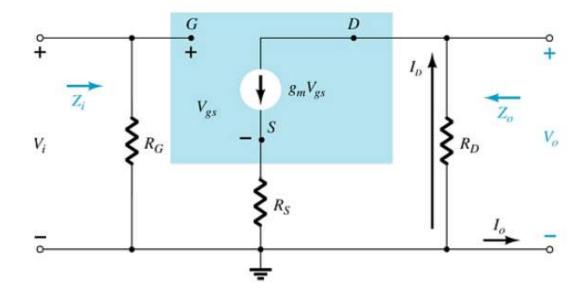

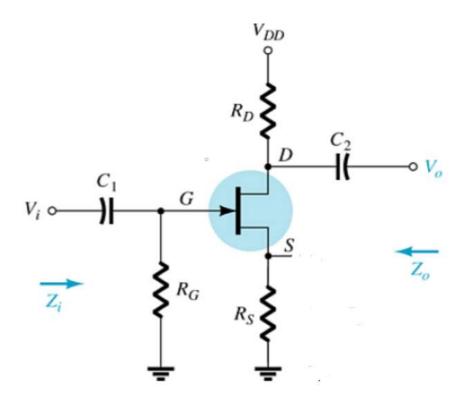

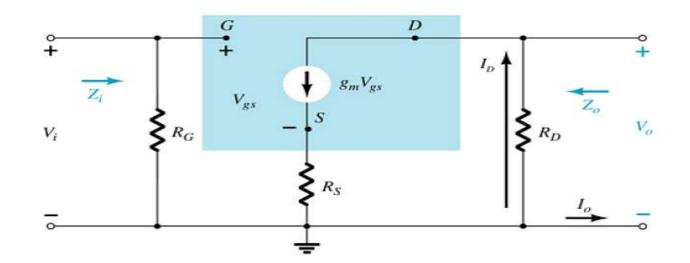

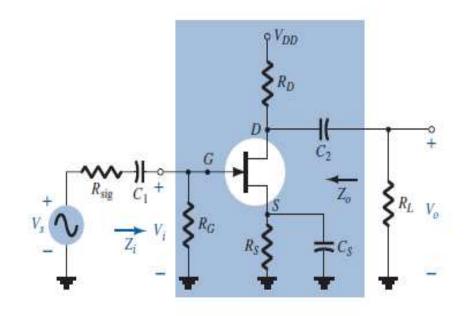

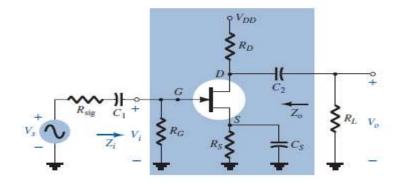

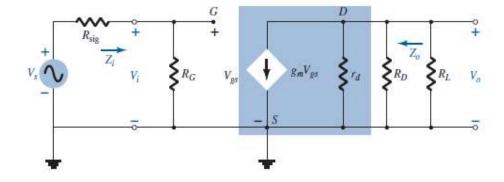

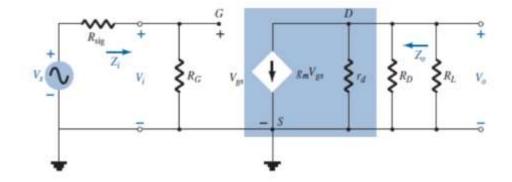

# AC analysis of JFET: 1) Fixed-Bias Configuration

The approach parallels the ac analysis of BJT amplifiers with a determination of the important parameters of  $Z_i$ ,  $Z_o$ , and  $A_v$  for each configuration.

$g_m$  and  $r_d$  are determined from the dc biasing arrangement

Substituting the JFET ac equivalent circuit unit into the network

Redrawn network

JFET fixed-bias configuration.

### **Input impedance Zi of JFET:**

$$Z_i = R_G$$

the infinite input impedance at the input terminals of the JFET.

### Output impedance Zo Of JFET:

**Z<sub>0</sub>** Setting  $V_i = 0$  V as required by the definition of  $Z_o$  will establish  $V_{gs}$  as 0 V also. The result is  $g_m V_{gs} = 0$  mA, and the current source can be replaced by an open-circuit equivalent . The output impedance is

$$Z_{o} = R_{D} \| r_{d} \|$$

$$g_{m}V_{gs} = 0 \text{ mA}$$

$$P_{d} = R_{D} \| r_{d} \|$$

$$R_{D} = R_{D} \| r_{d} \|$$

$A_V$  Solving for  $V_o$  in Fig. we find

$$V_o = -g_m V_{gs}(r_d || R_D)$$

but  $V_{gs} = V_i$

and  $V_o = -g_m V_i(r_d || R_D)$

so that

$$A_{v} = \frac{V_{o}}{V_{i}} = -g_{m}(r_{d} \| R_{D})$$

If  $r_d \geq 10R_D$ ,

$$A_{v} = \frac{V_{o}}{V_{i}} = -g_{m}R_{D}$$

$$r_{d} \ge 10R_{D}$$

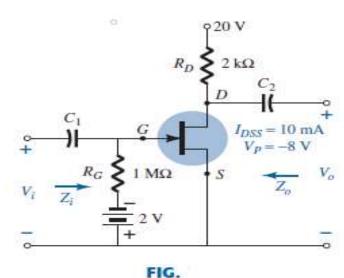

**EXAMPLE** The fixed-bias configuration of Example 1 had an operating point defined by  $V_{GS_Q} = -2 \text{ V}$  and  $I_{D_Q} = 5.625 \text{ mA}$ , with  $I_{DSS} = 10 \text{ mA}$  and  $V_P = -8 \text{ V}$ . The network is redrawn as Fig. with an applied signal  $V_i$ . The value of  $y_{os}$  is provided as  $40 \mu\text{S}$ .

- a. Determine  $g_m$ .

- b. Find  $r_d$ .